Это

фрагмент

учебного

пособия по

системе Electric VLSI Design System

Оригинальный

полный текст

учебника

смотрите

здесь: CMOSedu.com

Часть 2.

Компоновка и

симуляция

работы PMOS- и NMOS-транзисторов.

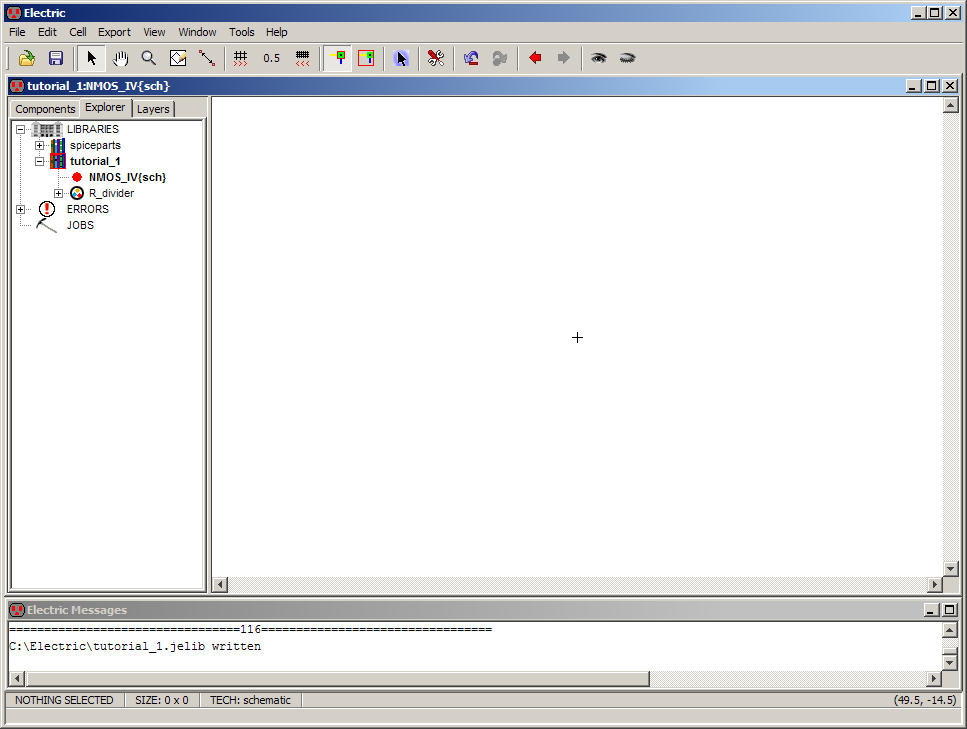

Для начала запустите программу Electric, чтобы открыть jelib-файл (File -> Open Library), в котором сохранены результаты предыдущего (вводного) урока. Вот он: tutorial_1.jelib

Если

появилось

окно запроса,

согласитесь с

выбором

параметров,

которые

установлены

в

загружаемой

библиотеке.

Сразу же пересохраните файл под другим именем (например, tutorial_2x.jelib) в ваш рабочий каталог.

В этот же каталог поместите файл C5_models.txt для SPICE-симулятора (при условии, что он на вашем компьютере есть и работает).

Этот

файл

содержит

параметры MOSFET-модели

для C5

процесса.

После

этого создайте

новую ячейку

(Cell -> New cell) типа schematic, дайте ей имя

NMOS_IV.

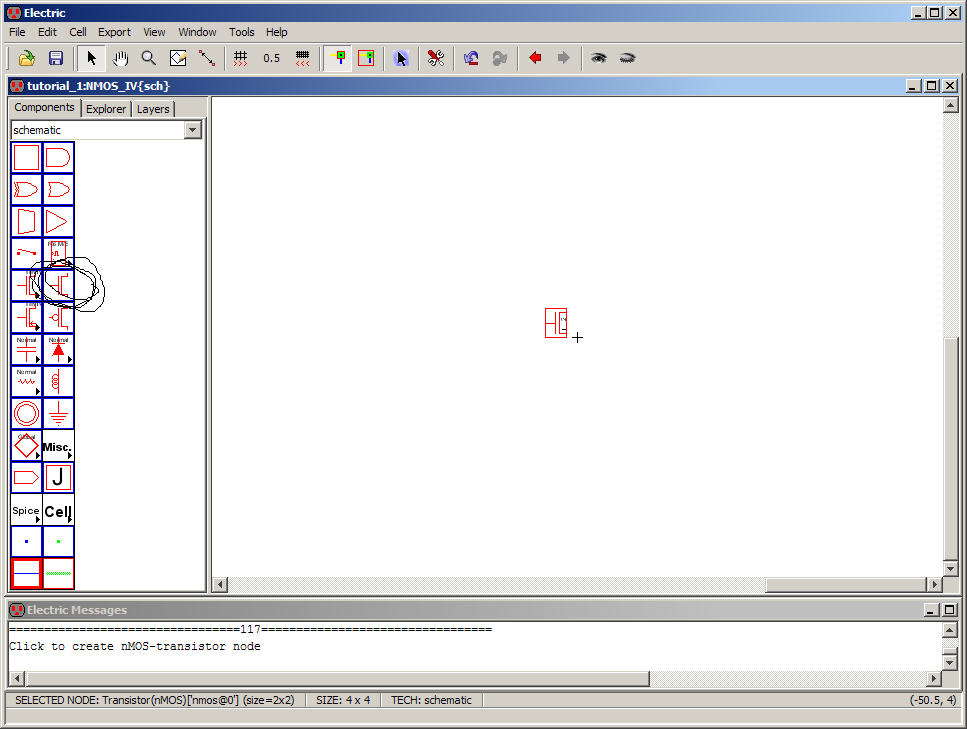

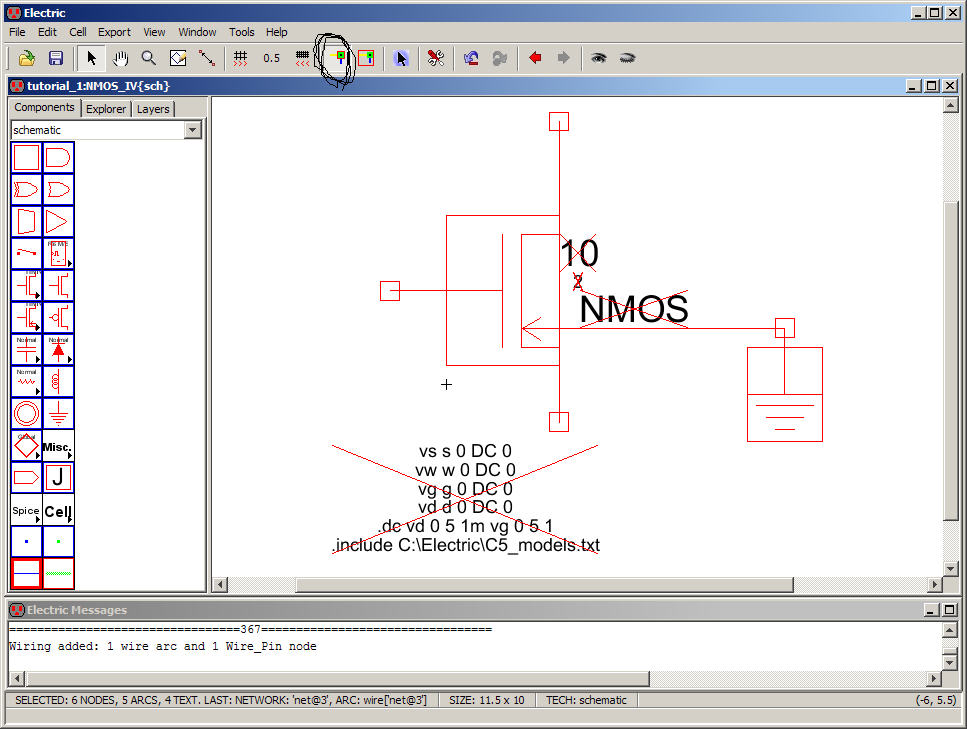

Перейдите

на вкладку Components и

выберите

элемент NMOS (на

рисунке

снизу обозначен

грязным

кружком)

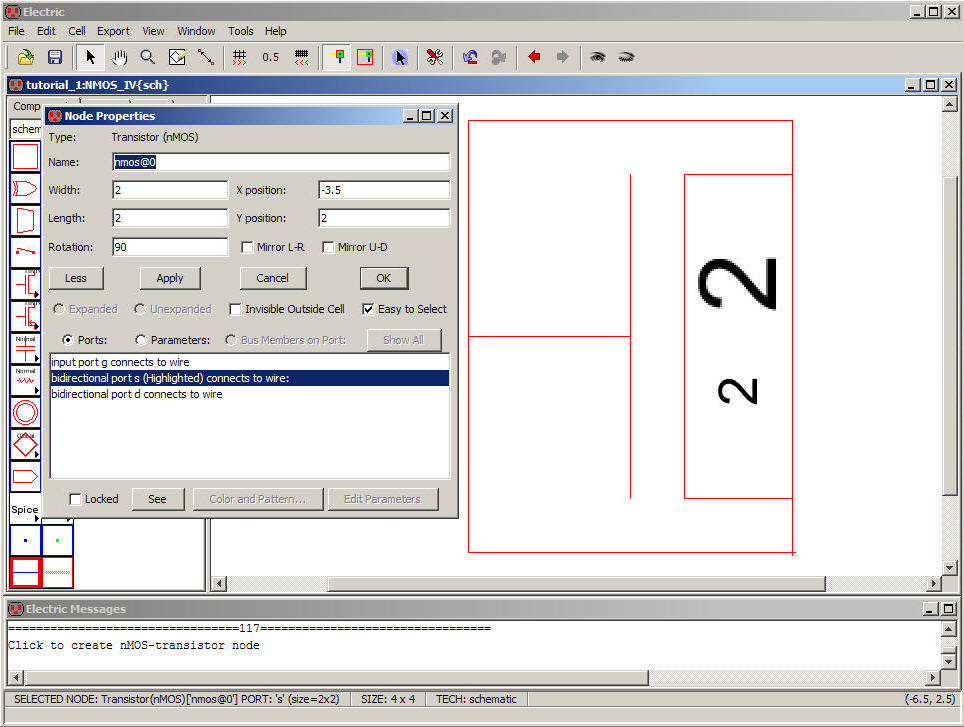

Увеличьте

элемент до

границ окна (Window -> Fill window) и

начинайте

редактировать

его свойства

(Edit -> Properties ->

Object properties)

Установите

ширину

устройства

равной 10 мкм, а

длину

оставьте

равной 2.

Нажмите ОК

для выхода.

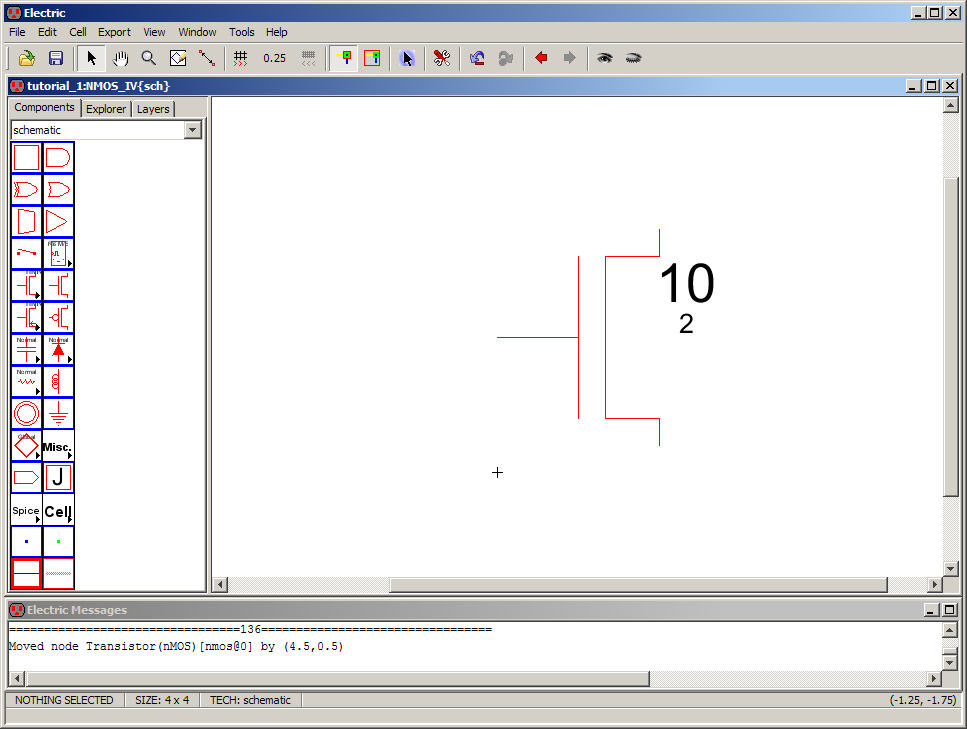

Потренируйтесь

в

редактировании,

повороте и

перемещении

текстовых

надписей

возле MOSFET-элемента

(Ctrl+I вам в

помощь).

Обратите

внимание:

выравнивание

сетки может

быть

уменьшено до

0.25, так что

элемент

может слегка

сместиться

от центра.

Измените

выравнивание

сетки (кнопки

на верхней

панели) к

значению 0.5.

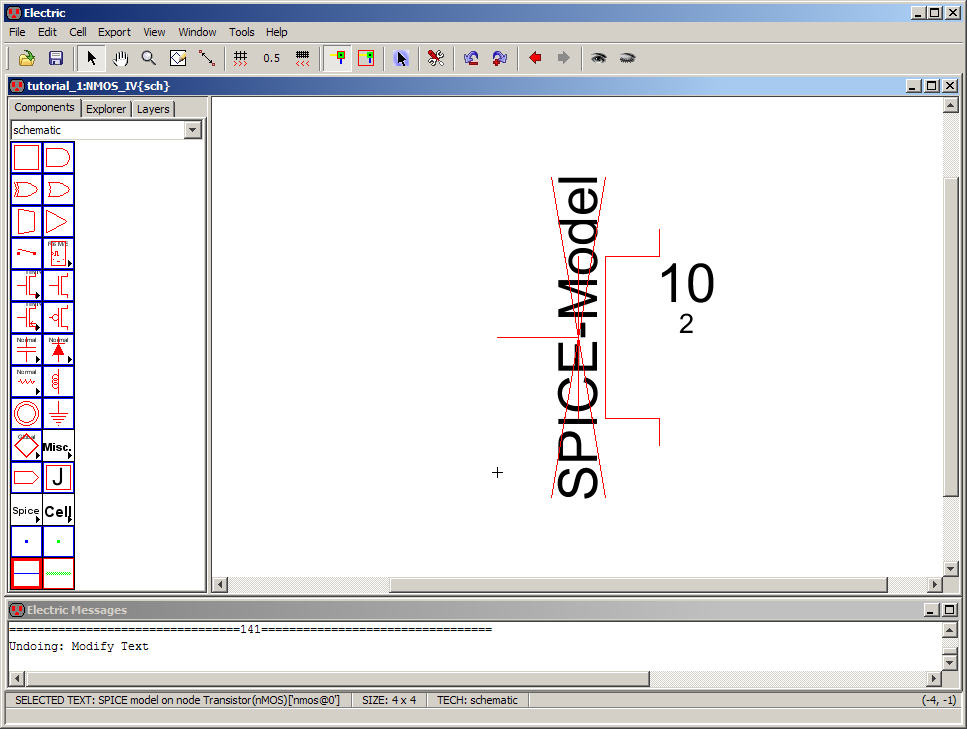

Теперь выберите элемент NMOS и войдите в Tools -> Simulation (Spice) -> Set Spice Model.

Вы

получите

что-то такое:

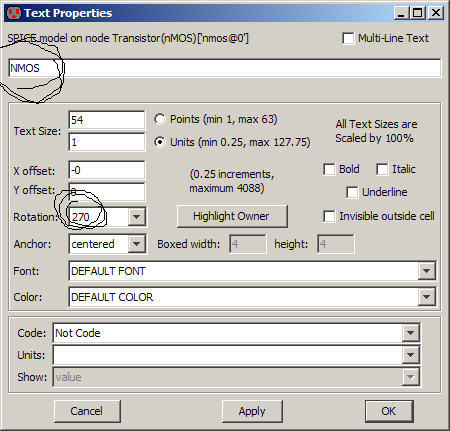

Отредактируйте

текст SPICE-модели,

используя Ctrl+I.

Введите

имя NMOS для NMOS-структуры

(ну и потом PMOS имя

для PMOS-структуры).

Эти имена

будут

ассоциированы

затем с

файлом C5_model.txt.

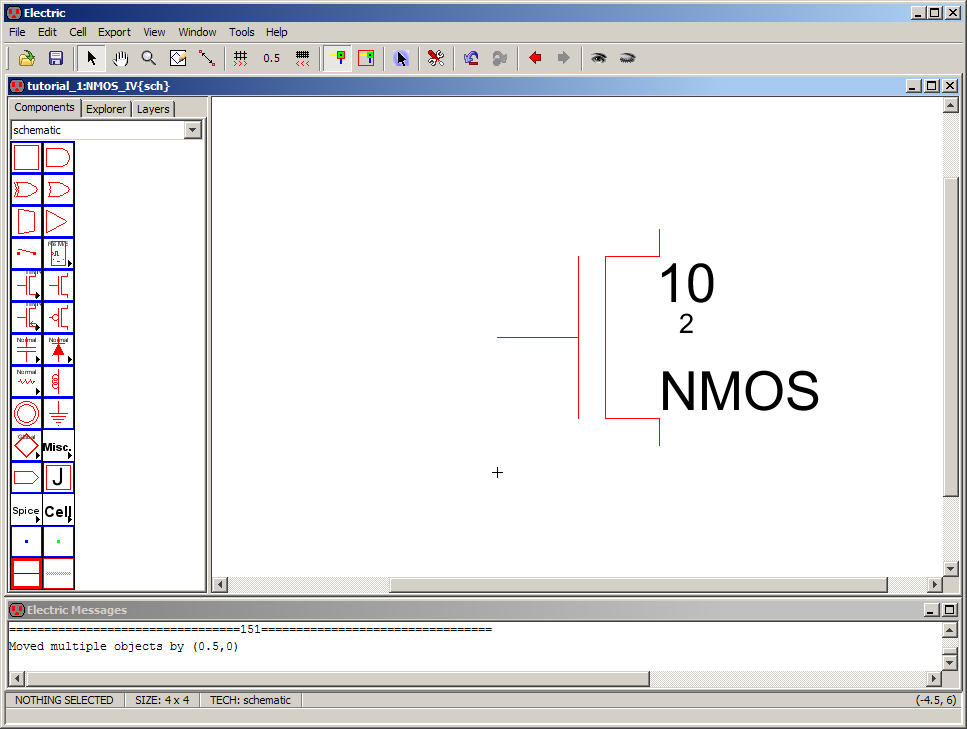

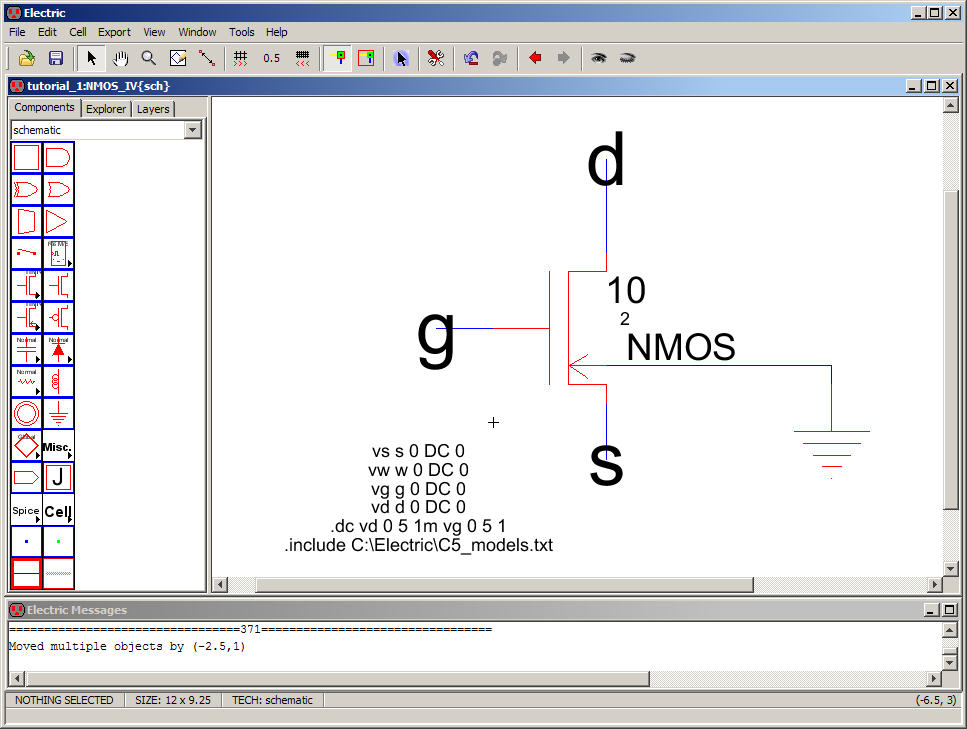

Переместите SPICE-имя в более удобную позицию, как показано ниже

С этого момента мы можем просто копировать этот узел, чтобы не выполнять эти шаги, когда мы размещаем NMOS-устройство.

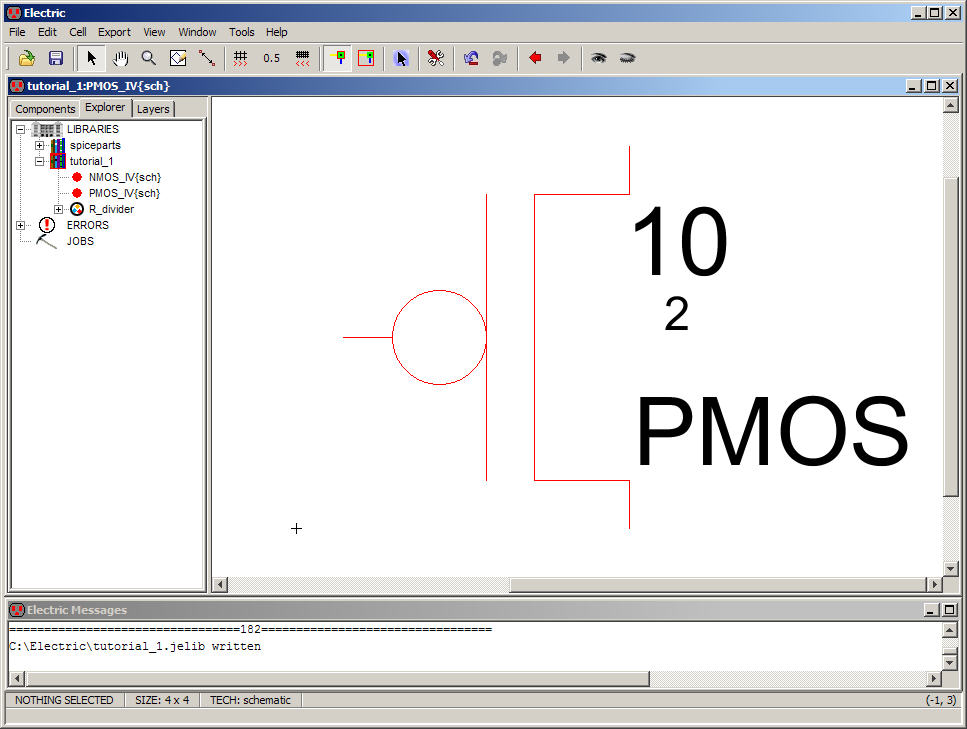

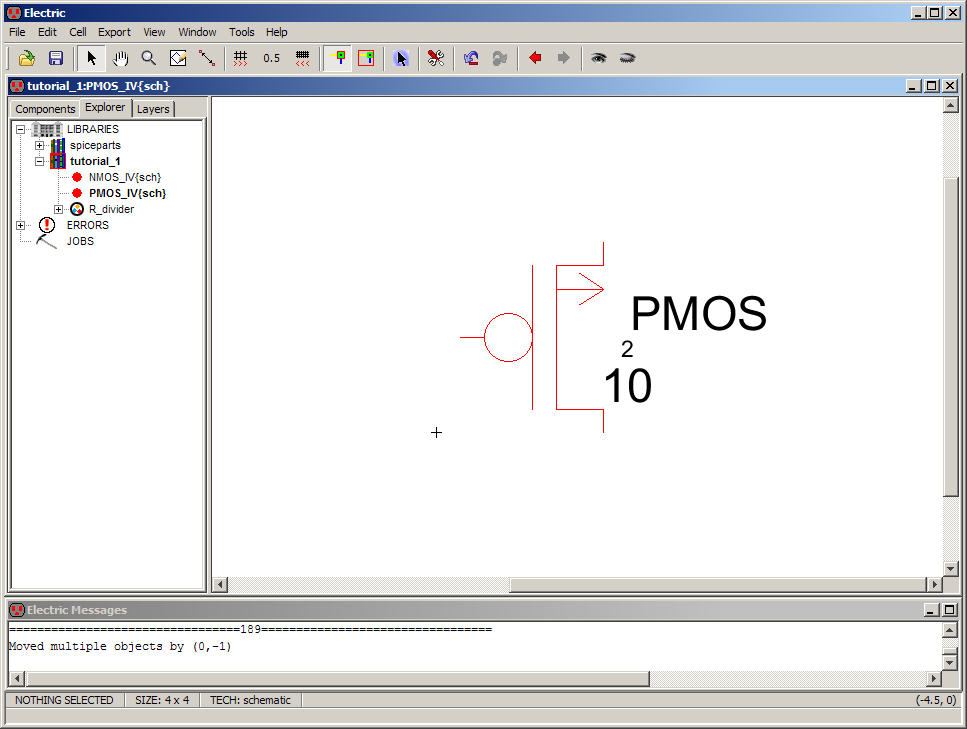

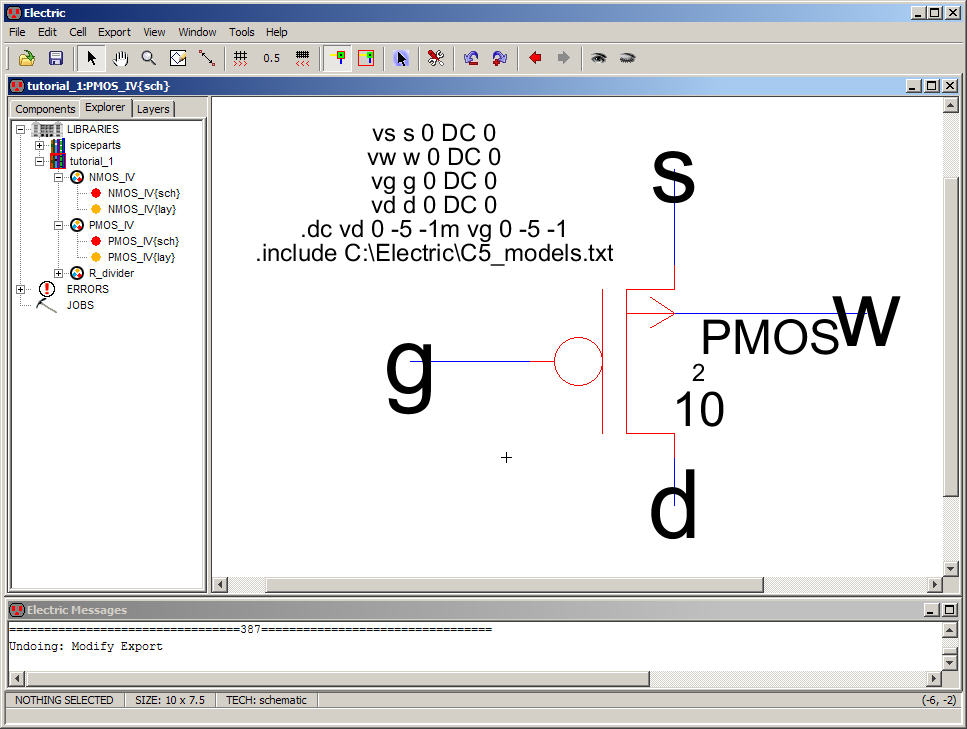

Точно

так, как вы

создавали NMOS_IV-структуру,

сделайте

второй узел PMOS_IV.

Смотрите,

что должно

получиться:

Эти

символы

полезны для

изображения

элемента, но

мы хотим

иметь доступ

ко всем выводам

транзистора,

включая

"корпус"

устройства.

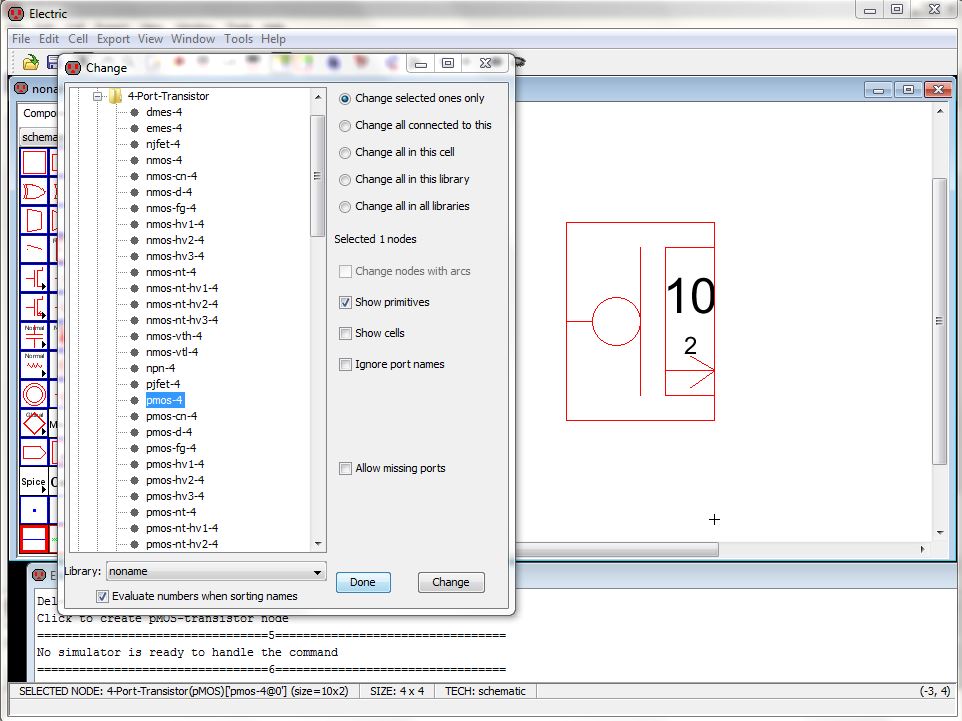

В

нашей PMOS_IV ячейке

выберите PMOS элемент

и войдите в

меню Edit -> Change или

просто

нажмите

клавишу C.

Появится

окошко Change. Вот и

измените в

нём тип

устройства

на 4-портовый

транзистор pmos-4. Нажмите Apply, а затем Done.

Заметим,

что корпус

(здесь это n-карман)

находится

рядом с

истоком PMOS транзистора.

Поскольку

рисуют

корпус и

исток сверху PMOS-устройства,

а сток снизу,

перевернём

элемент с

помощью

команды Edit -> Mirror -> Up <--> Down.

Смотрите

результат:

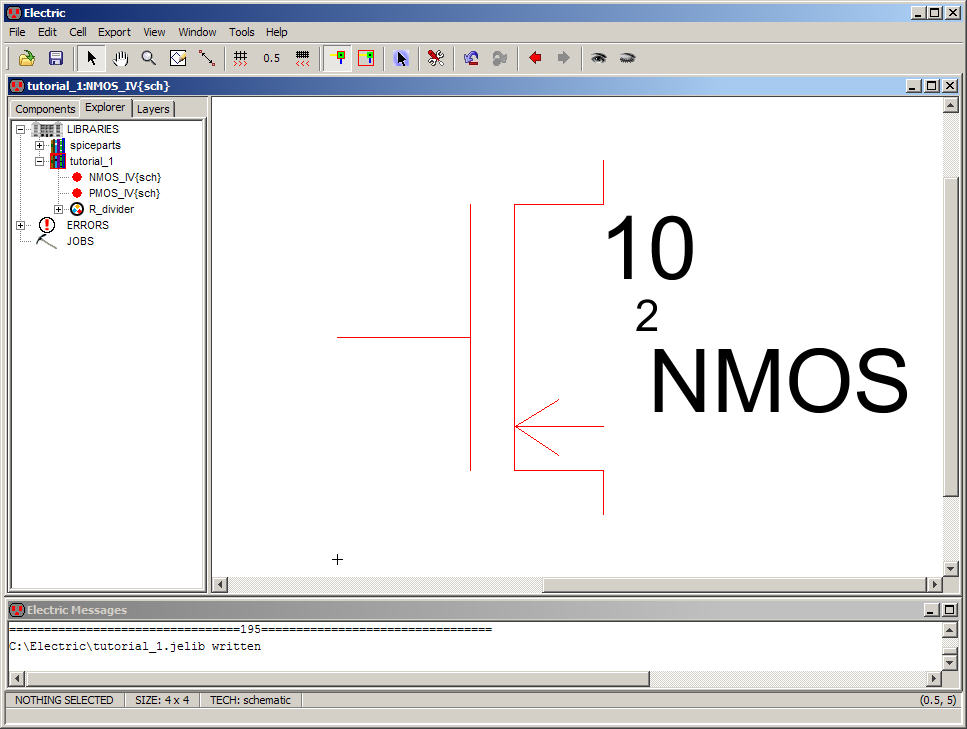

Не

забудем

отредактировать

и NMOS_IV ячейку.

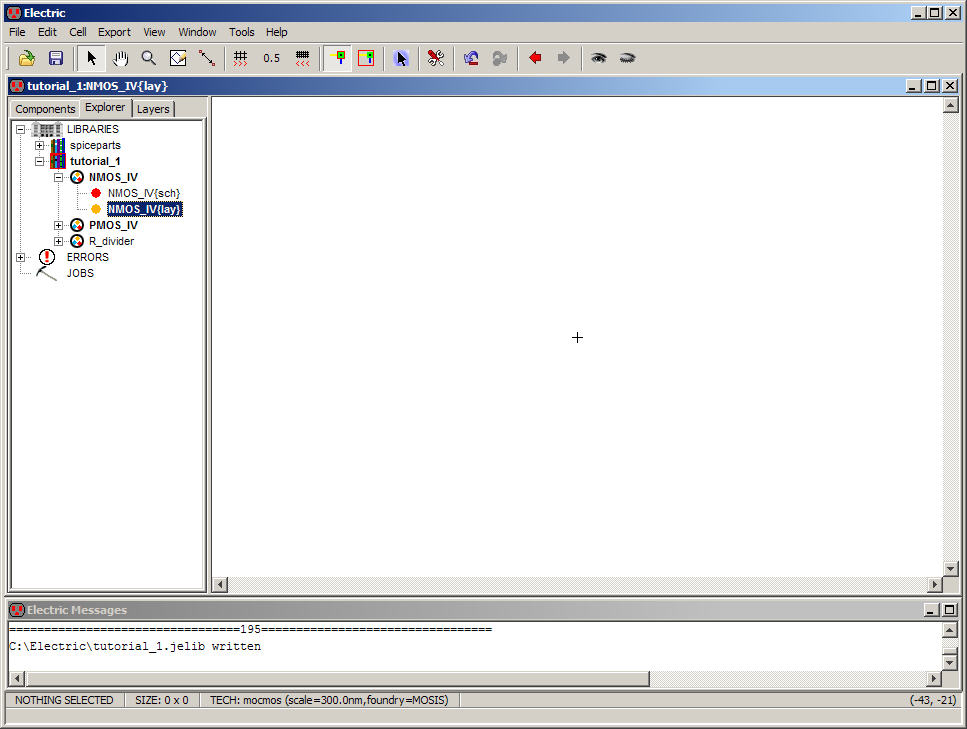

Теперь

создадим layout views

(представления

компоновки)

для наших

ячеек.

Создадим две

новых ячейки

(Cell -> New Cell) для NMOS и PMOS в

технологии mocmos. Войдём в NMOS_IV{lay}.

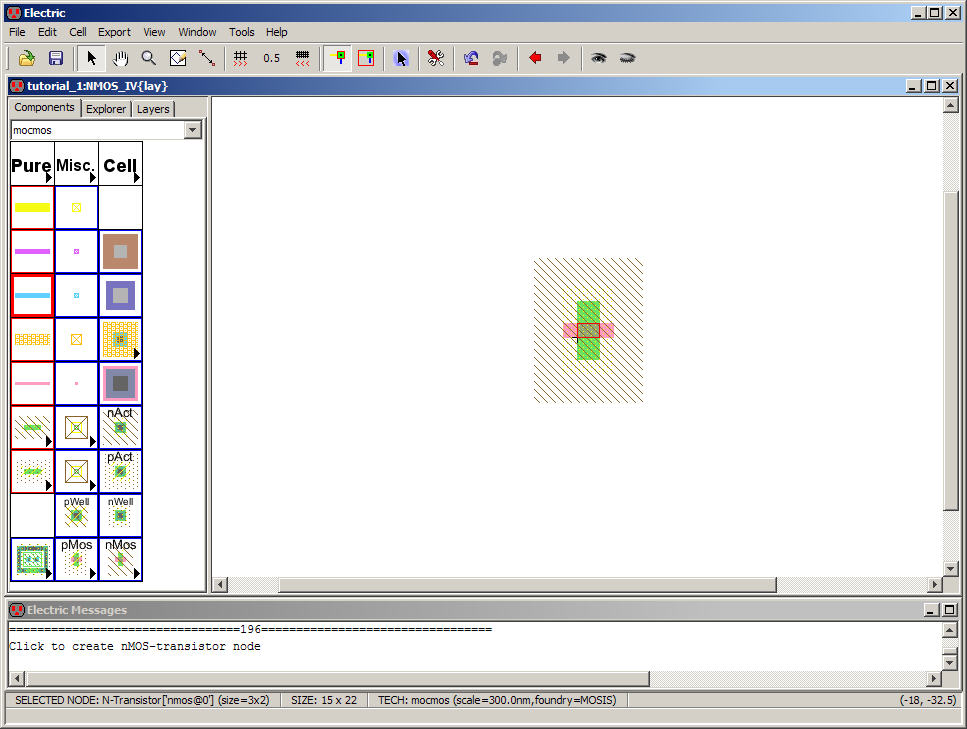

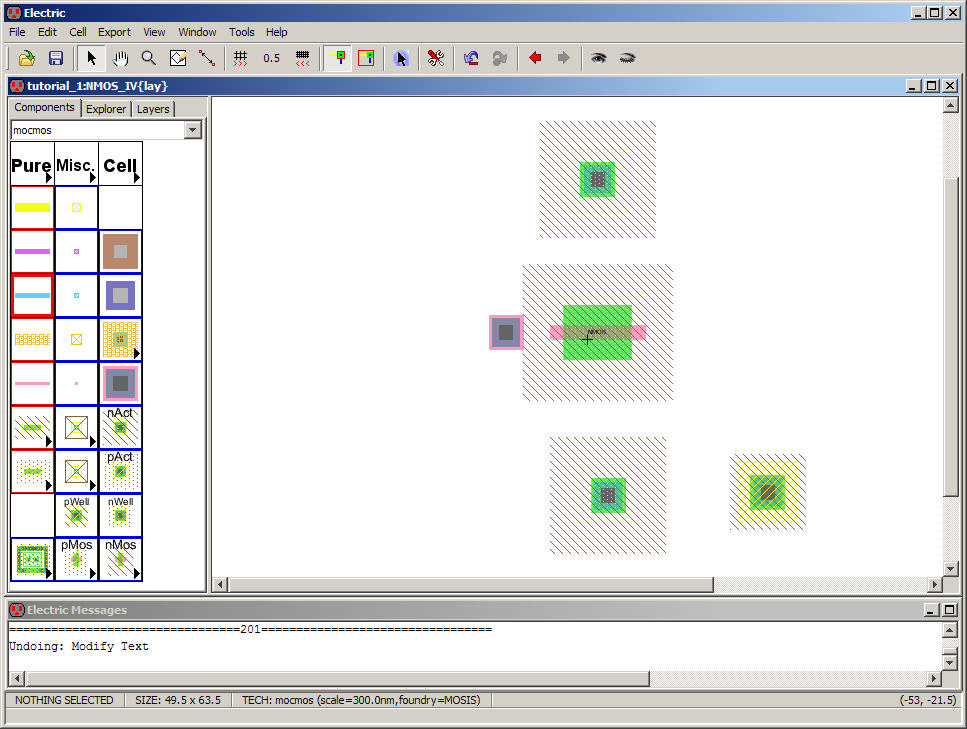

Перейдём

на вкладку components (слева)

и выберем nMos-компонент

в нижнем

правом углу,

как показано

ниже.

Это

компоновка NMOS устройства

состоящего

из p-кармана,

активной

области n-типа

(зелёный) и поликремниевого

затвора

(розовый).

Подсвеченная

рамка

показывает,

что компонент

выбран.

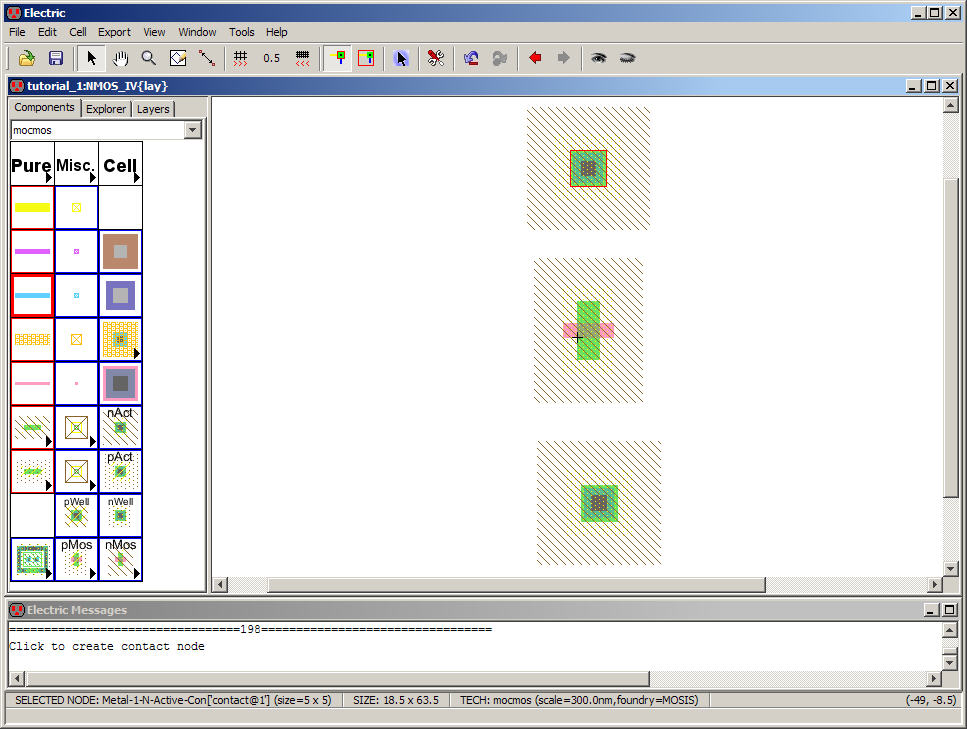

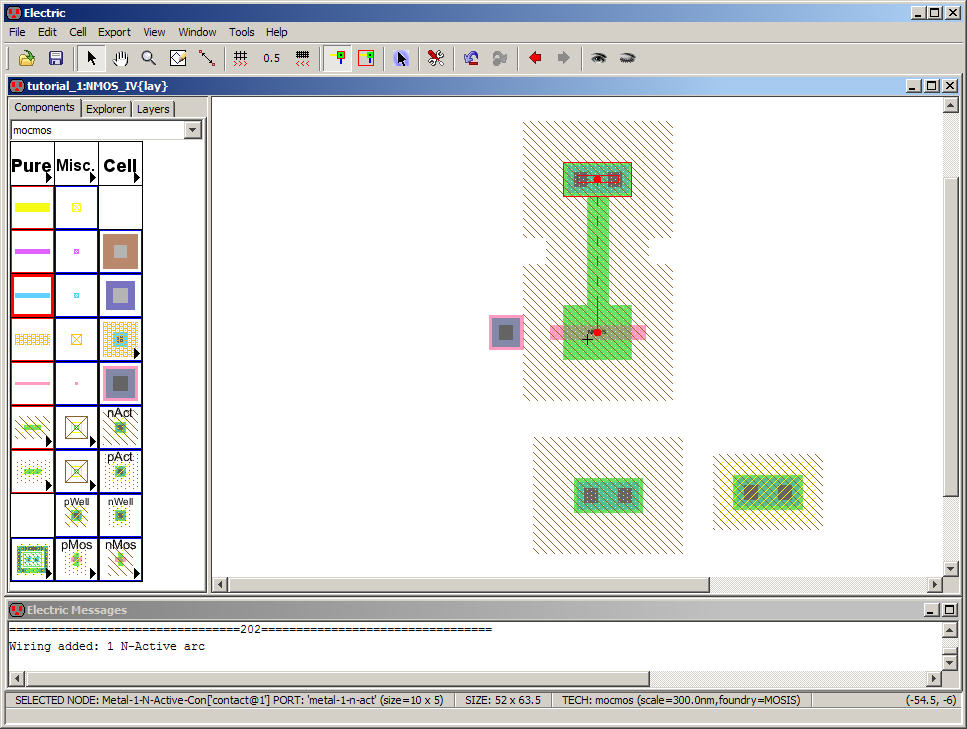

Далее

добавим nAct-компоненты

как показано

ниже.

Они

будут образовывать

MOSFET-транзистор,

формируя

исток и сток

устройства.

Они

также будут

обеспечивать

контакт с металлом

(metal1 Arcs)

для истока и

стока MOSFET.

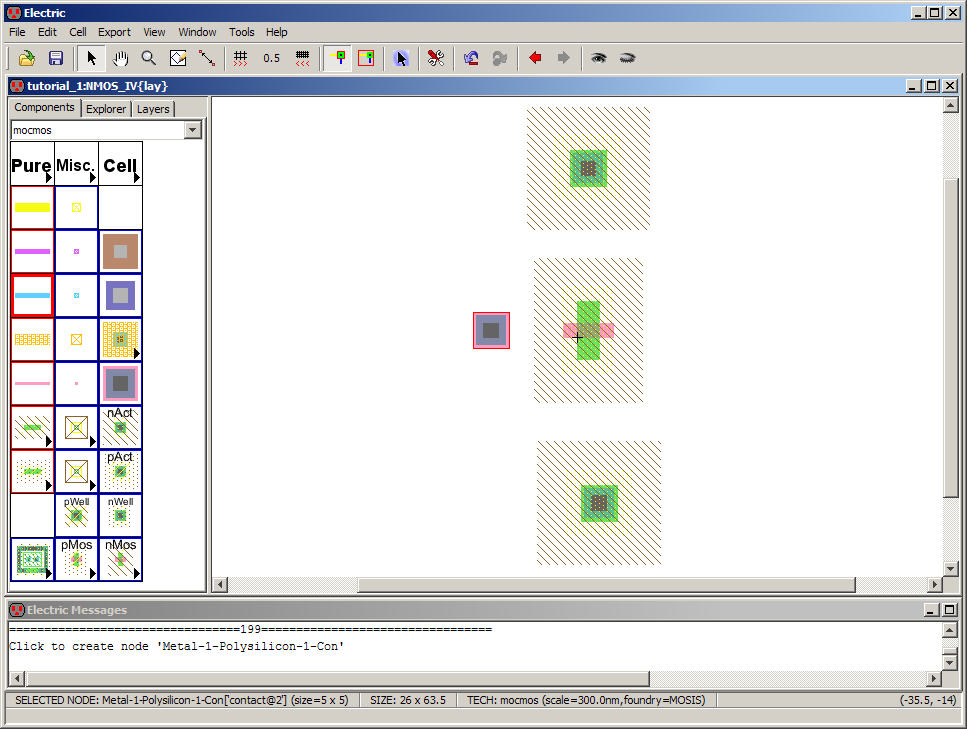

Теперь

добавим metal1 для

контакта к poly1 как

показано

ниже.

Из

этого должен

будет

получиться

затвор MOSFET.

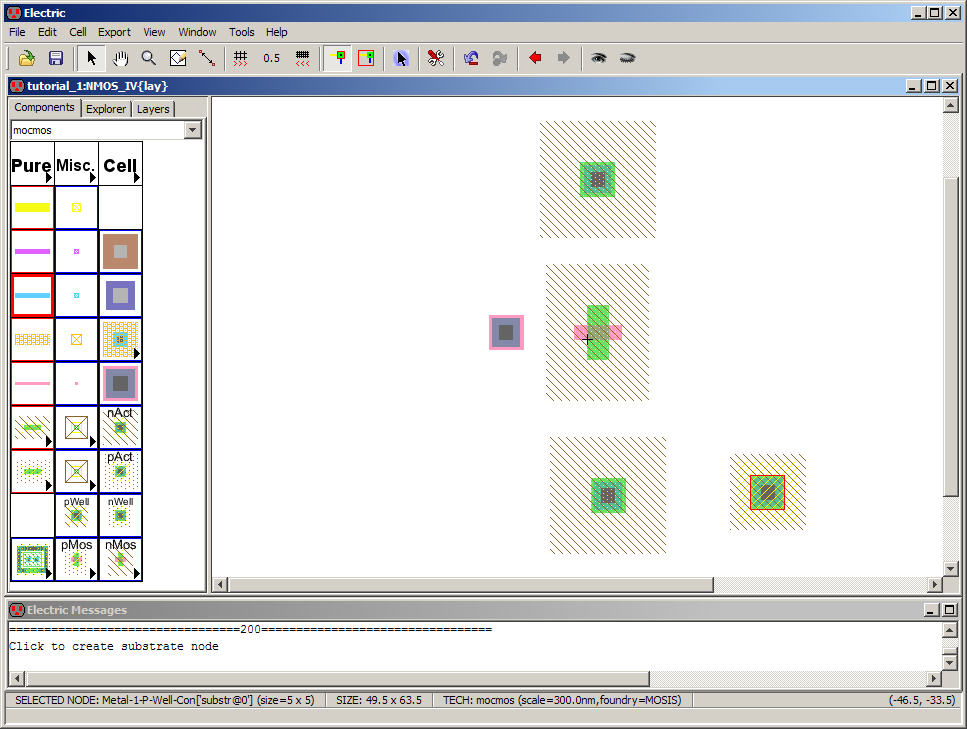

Наконец,

поставим

контакт к

"корпусу" для NMOS устройства,

это будет pWell Node.

Итак,

всё готово

для

соединения

элементов с

помощью

мостиков

металлизации.

Чтобы

изменить

размер

компонентов,

используйте Edit -> Properties ->

Object Properties

(либо Ctrl+I)

Перейдите

к NMOS компоненту

и сделайте

его ширину

равной 10.

Далее,

оставляя

выбранным NMOS-компонент,

откройте

меню Tools -> Simulation (Spice) -> Set Spice

Model� и

установите

имя модели NMOS (если

этого не

сделать,

невозможно

будет моделировать

компоновку).

Используйте

при выборе

текста Ctrl-клик.

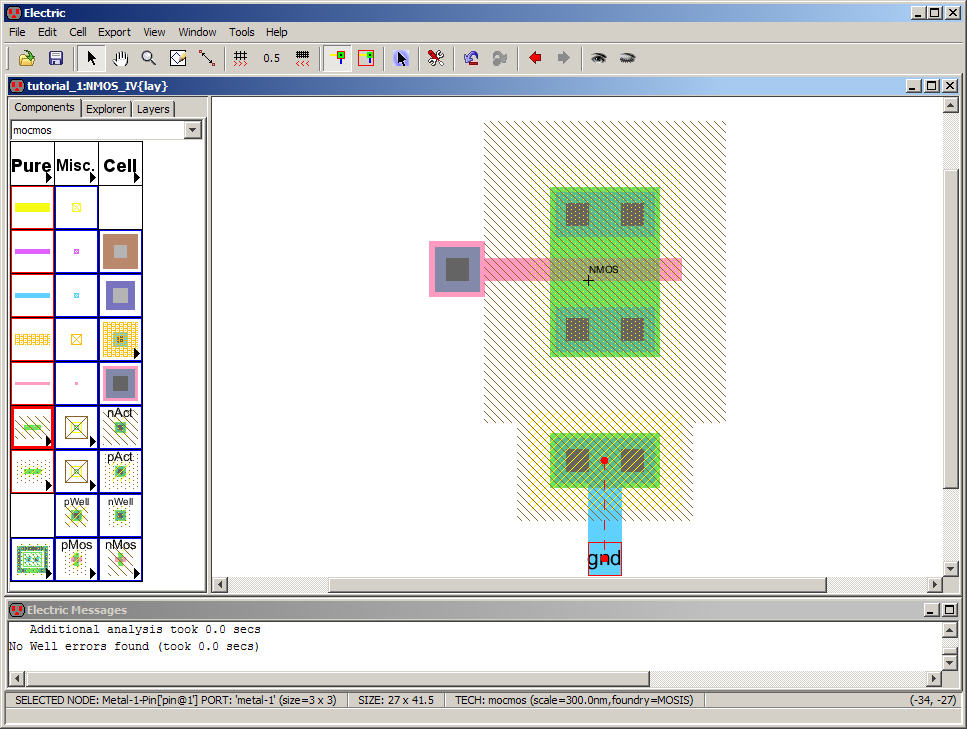

Результат

показан ниже:

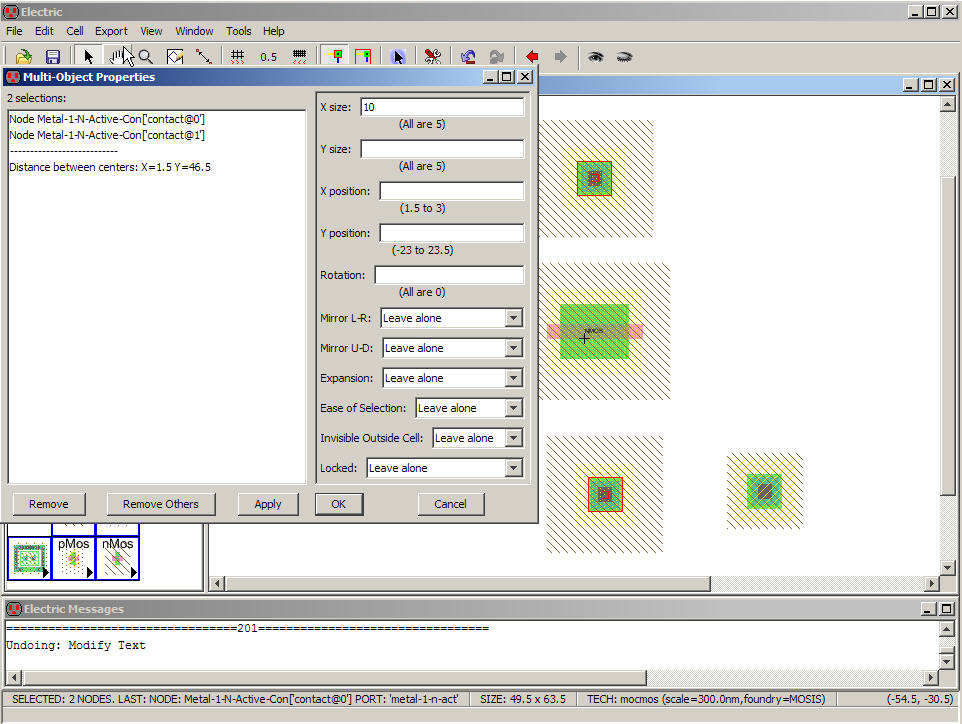

Затем

выберите оба nAct-компонента.

Для выбора

нескольких

элементов

держите

нажатой

клавишу Shift.

В

окне

редактирования

свойств

сделайте X size равным 10,

так же, как и

для

предыдущего

элемента MOSFET.

Последний

шаг перед

металлизацией:

изменим X-size для pWell компонента

� сделаем его

тоже равным 10.

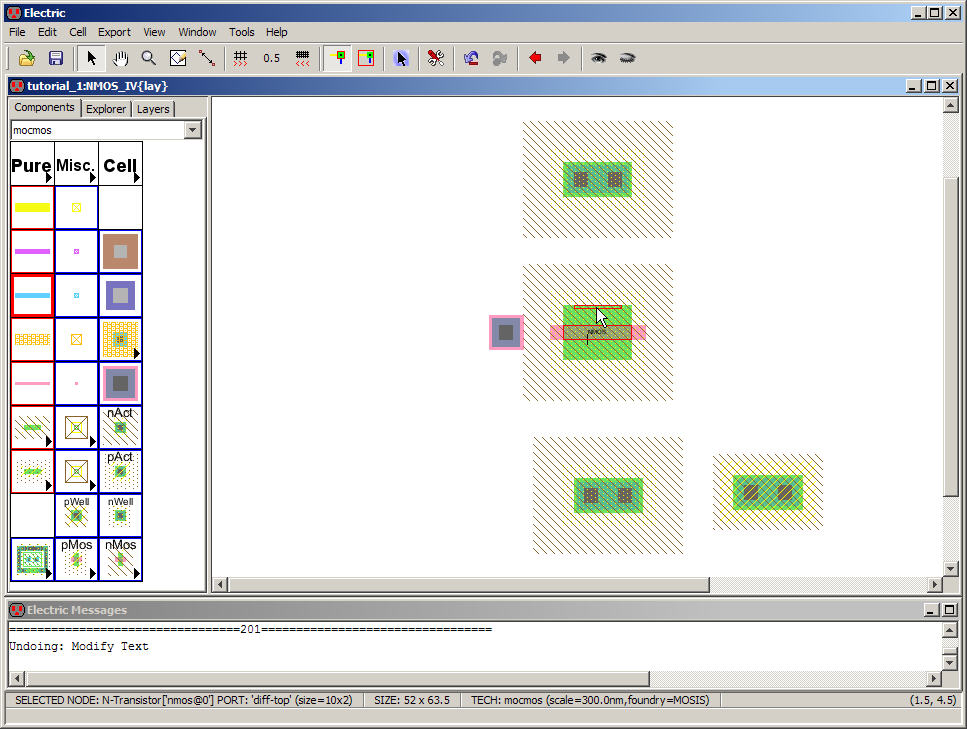

Теперь,

используя

левую

клавишу мыши,

выберем

верхний порт NMOS-компонента.

Переместим

мышь вверх до

nAct-компонента

и кликнем по

нему правой

клавишей.

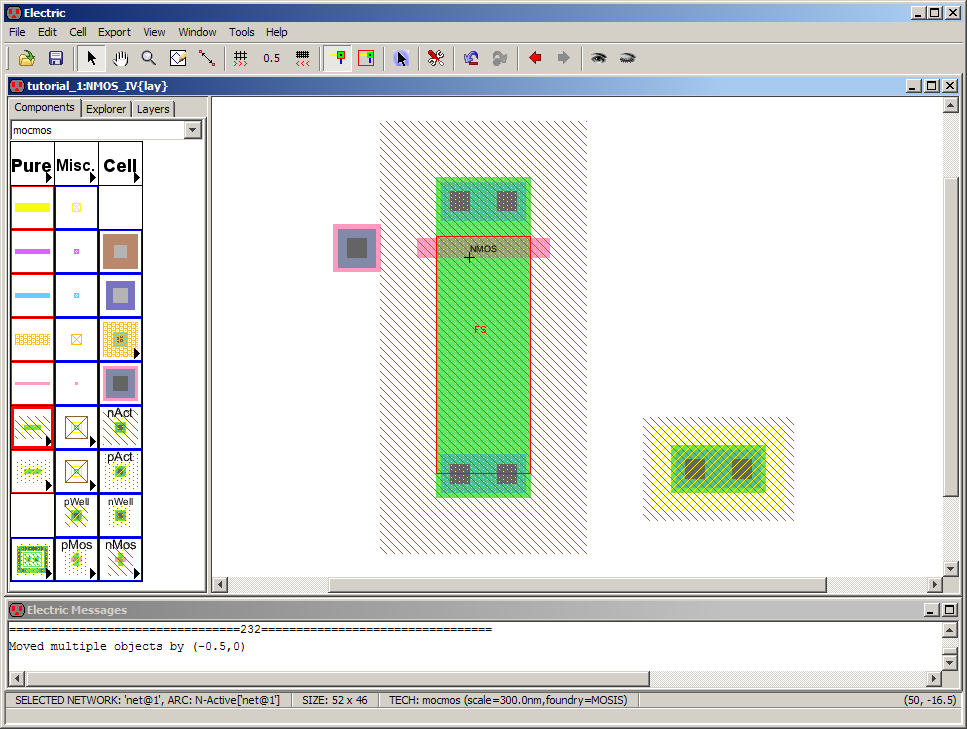

Результат

показан ниже.

Между

компонентами

протянулся n-канал.

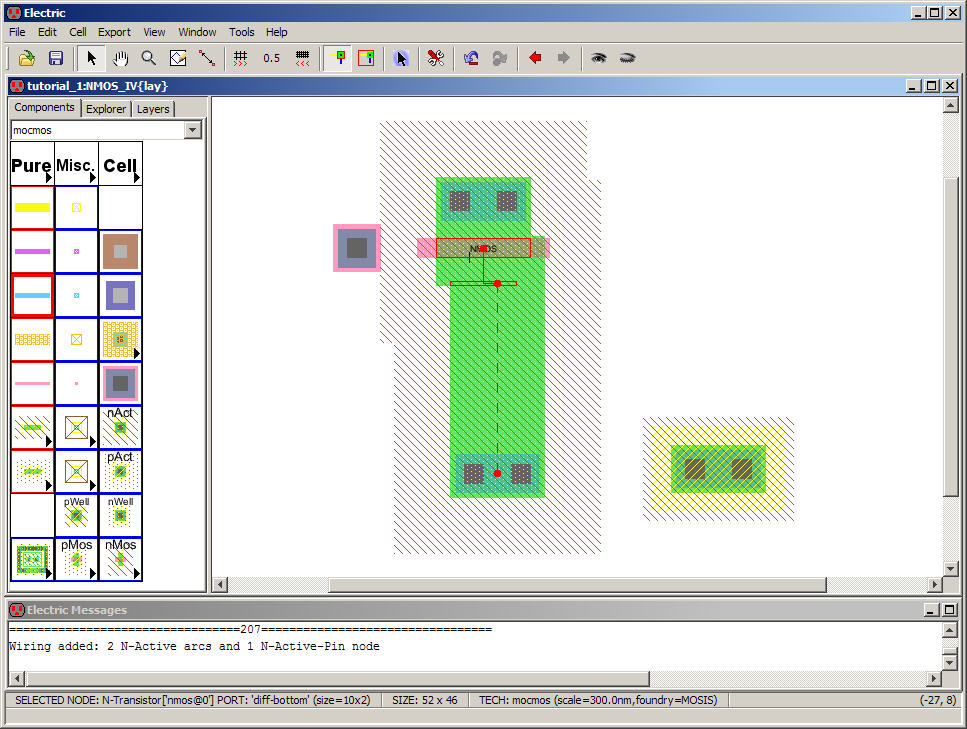

Переместим

этот nAct-компонент

вниз, как

показано на

следующем рисунке.

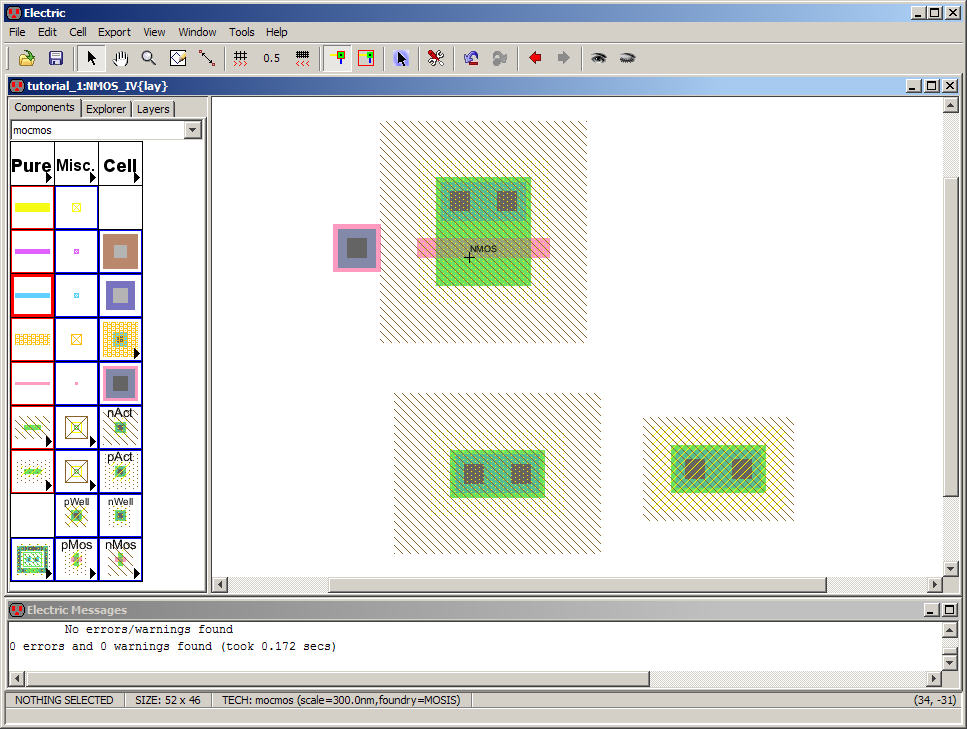

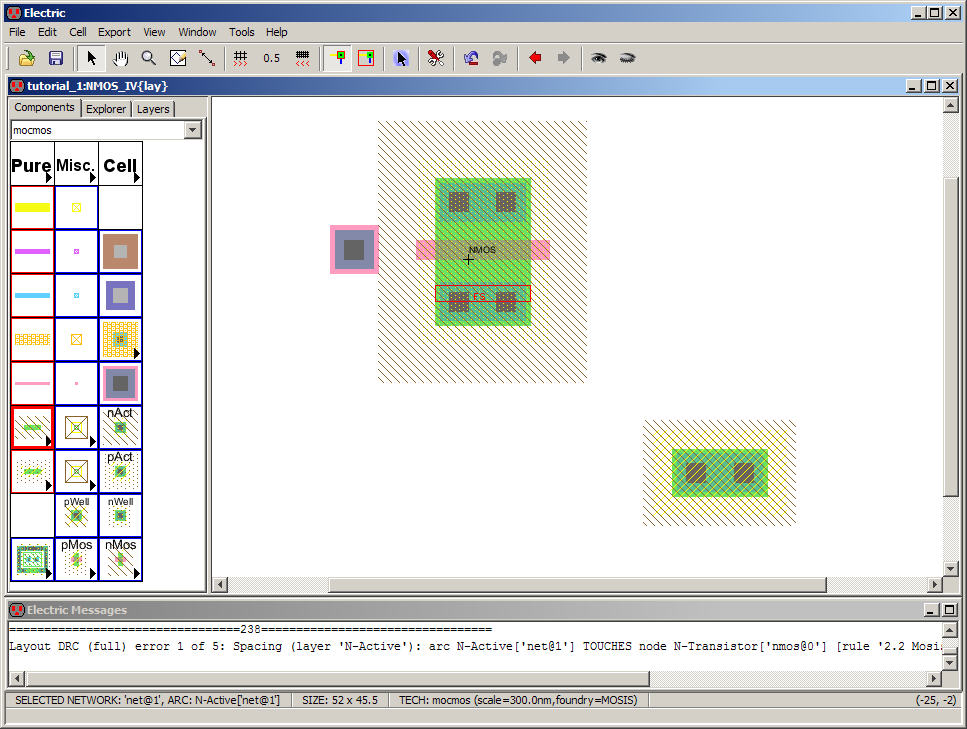

Проверим

ошибки

(Запустим DRC, клавиша F5). Если

есть ошибки,

перемещаем

компоненты (обычно

раздвигая

их), чтобы

ошибки

исчезли.

Соединяем

нижний nAct-компонент

с NMOS.

Ширина

полосы

изменилась, и

оба конца

линии

отмечены

точками.

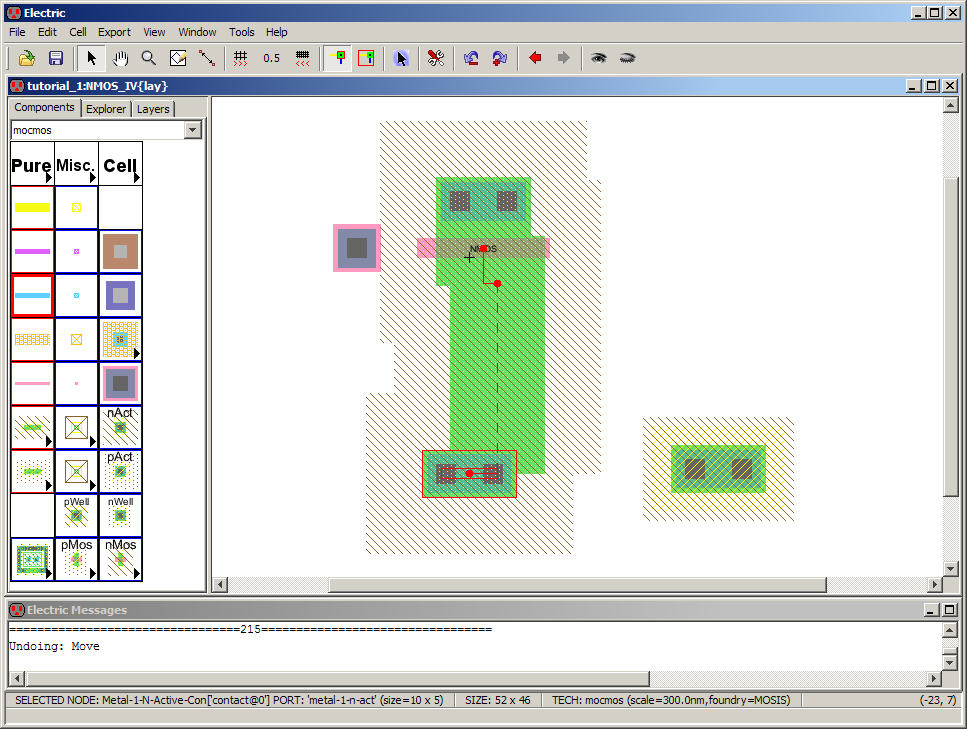

Если

выбрать

нижний nAct компонент

и

переместить

его влево,

будет следующее:

Если

мы продолжим

перемещать

этот узел, n-канал в

конечном

итоге будет

двигаться.

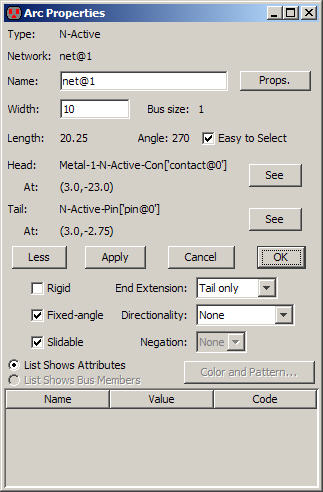

Это

поведение

связано с

свойствами Arc-компонента,

см. ниже.

Выбор

"Rigid" заставит Arc двигаться,

когда мы

будем

перемещать nAct-компонент.

Однако

вернём всё на

место (Ctrl+Z).

Когда

Arc активна,

можно

использовать

клавиши-стрелки,

чтобы

перемещать Arc, пока он

не

выровняется

с узлом nMos, см. Ниже.

Вместо

того, чтобы использовать

стрелки,

можно также

использовать

мышь.

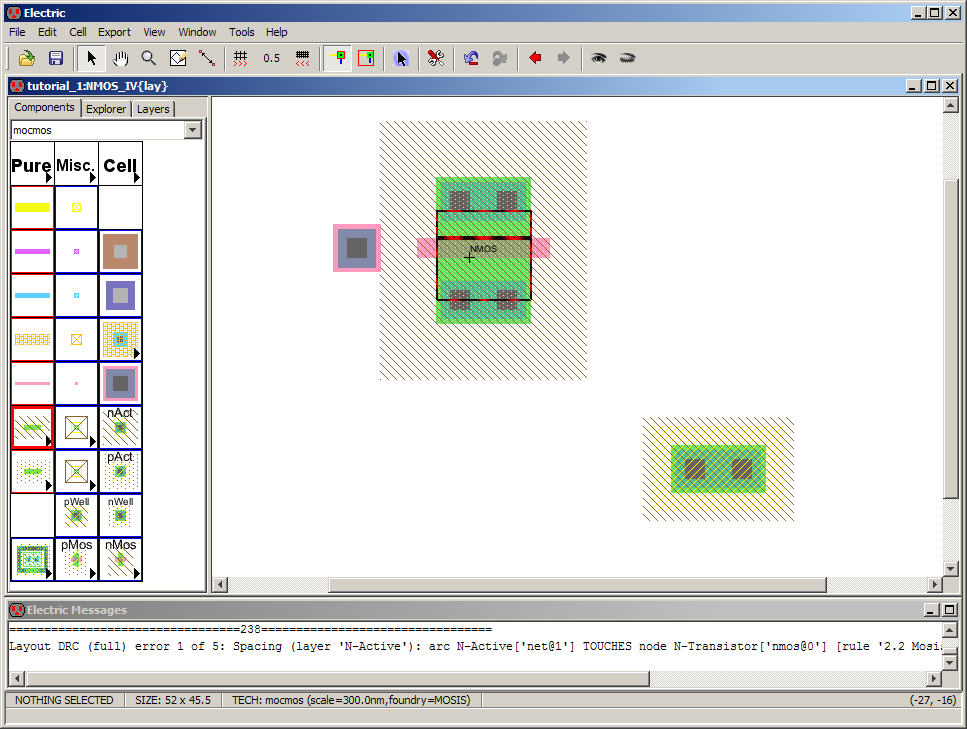

Сдвинем

нижний nAct-компонент

вверх на своё

место

(зеркально относительно

верхнего nAct-компонента)

и запустим DRC.

На рисунке

5 DRC ошибок.

Нажимаем

клавишу >

чтобы

перейти к

следующей

ошибке,

которые

обычно

возникают

из-за перекрывания

областей.

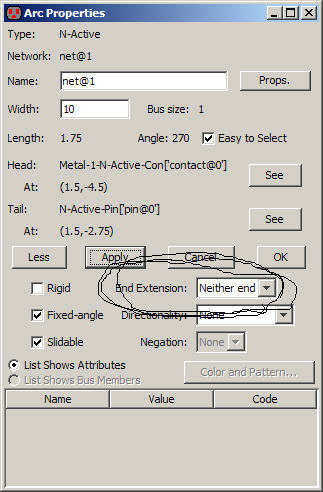

Исправим

ошибки.

Изменим

свойства Arc (Ctrl+I), а именно

для End Extension укажем

"Neither end"

как показано

внизу.

Вот

результат.

Сейчас

компоновка

прошла DRC.

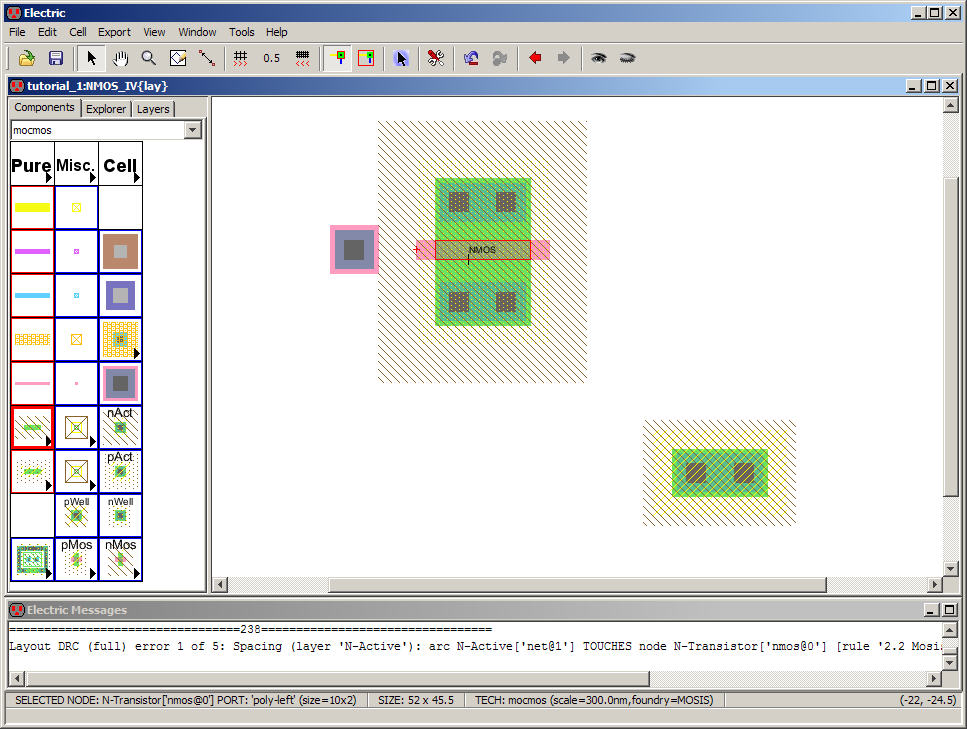

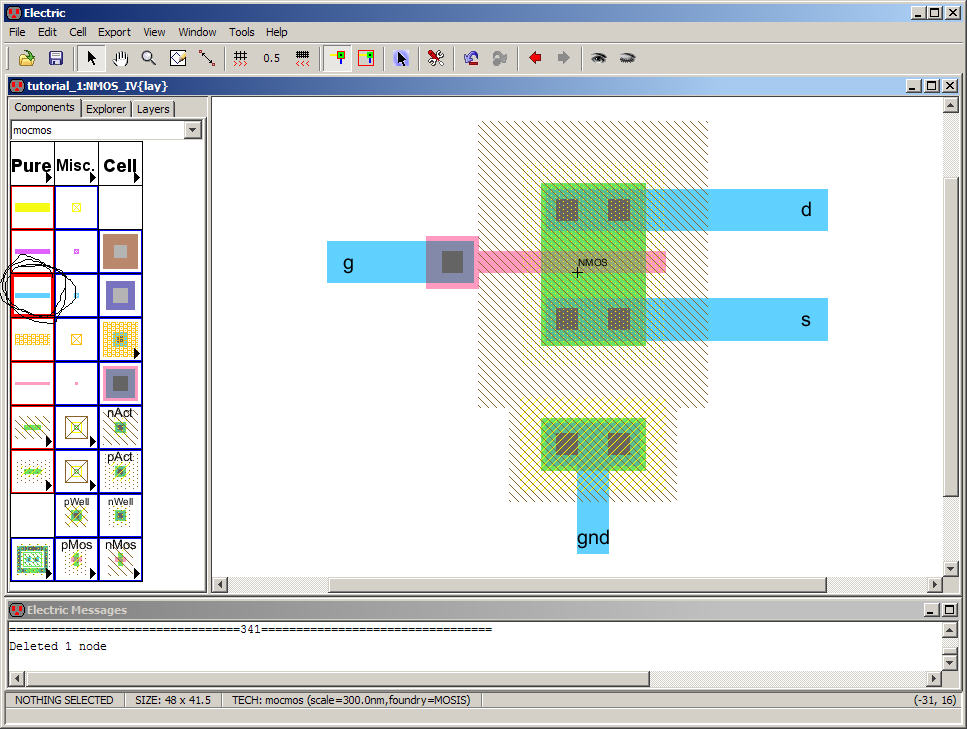

Соединим

затвор MOSFET с metal1-poly1-компонентом,

выбрав

вначале

левый poly1

порт

транзистора,

как показано

ниже.

Переместим

курсор на metal1-poly1

контакт и

нажмём

правую

клавишу мыши.

DRC ошибок

не даёт.

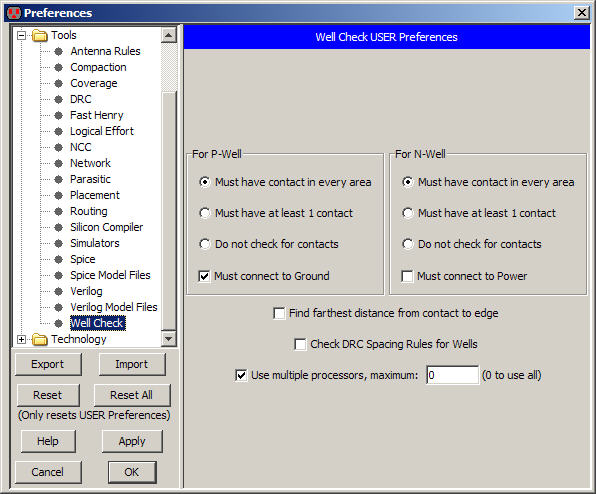

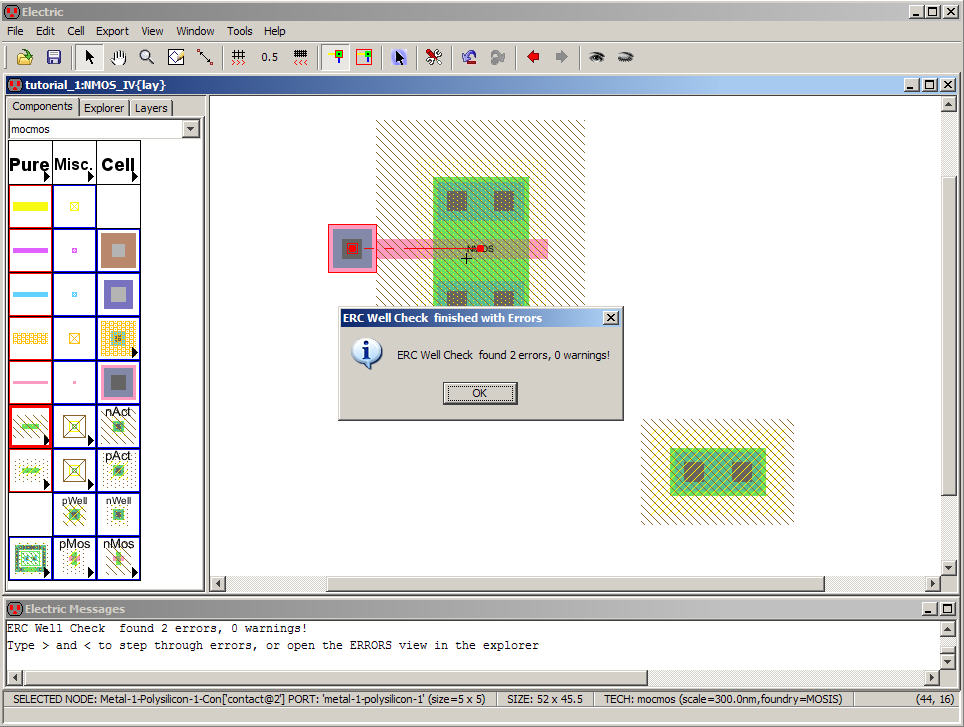

Давайте

не будем

забывать об ERC Well Check (Tools -> ERC -> Checks)

Чтобы

откорректировать

настройки,

войдите в File -> Preferences

-> Tools -> Well Check

Когда

мы выполняем

проверку кармана

на

вышеуказанной

схеме, мы

можем

получить две

ошибки:

одна

из них

связана с

тем, что в p-кармане,

окружающем NMOS-устройство,

нет контакта

с ячейкой;

вторая

- потому что

изолированный

узел pWell не

подключён к

земле, см.

ниже.

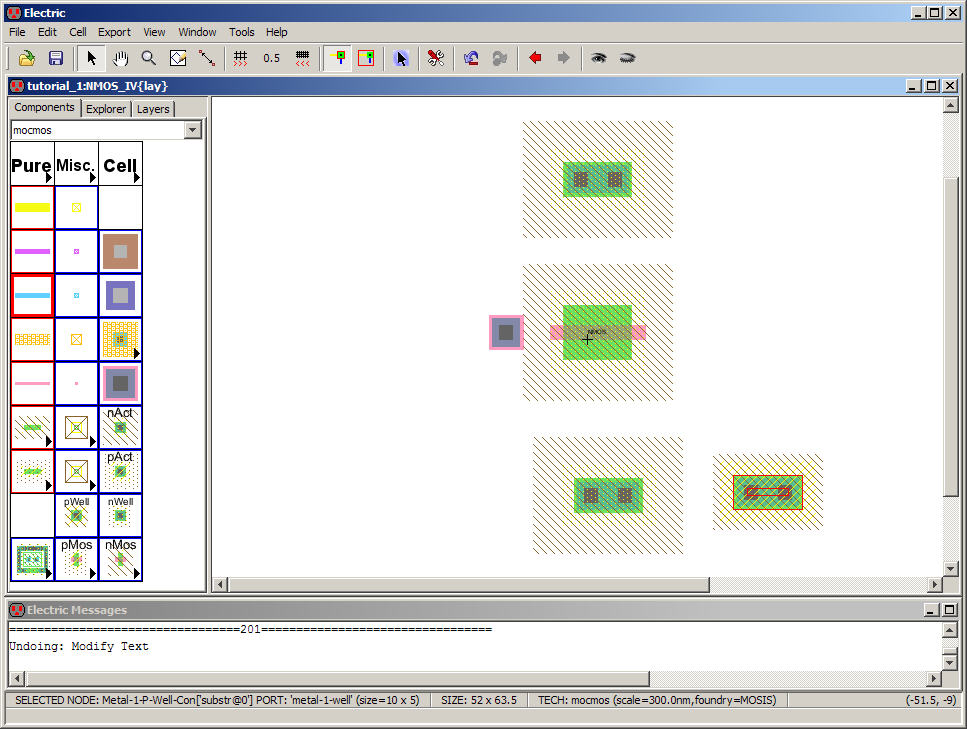

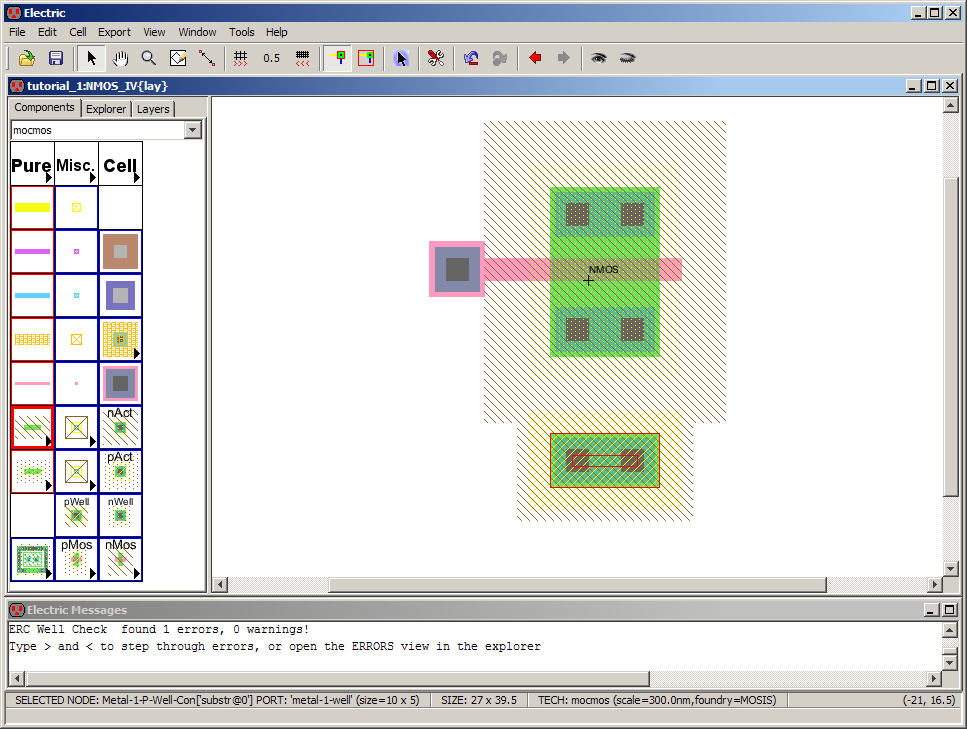

Переместим

pWell-компонент

так, чтобы он

перекрыл nMOS p-well слой,

как показано

ниже. Тем

самым

исправим первую

ошибку.

Выполните

проверку DRC и ERC

после

перемещения

этого узла,

чтобы не отображать

ошибки DRC и только

одну ошибку ERC.

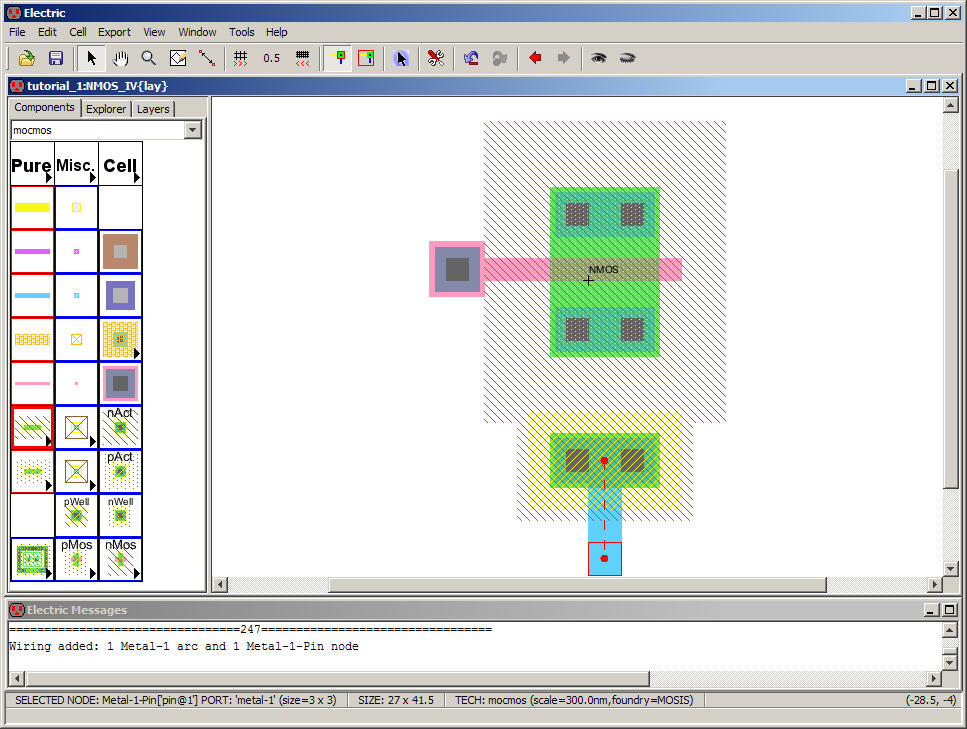

Чтобы

Electric знал, что

мы

собираемся

только

подсоединить

подложку к

земле,

переместите

курсор под

выбранным

узлом pWell и

нажмите

правую

кнопку мыши,

чтобы получить

следующее:

На

этом этапе вы

должны знать,

как выбрать добавленную

металлизацию

и как

изменить её

ширину и

завершитель.

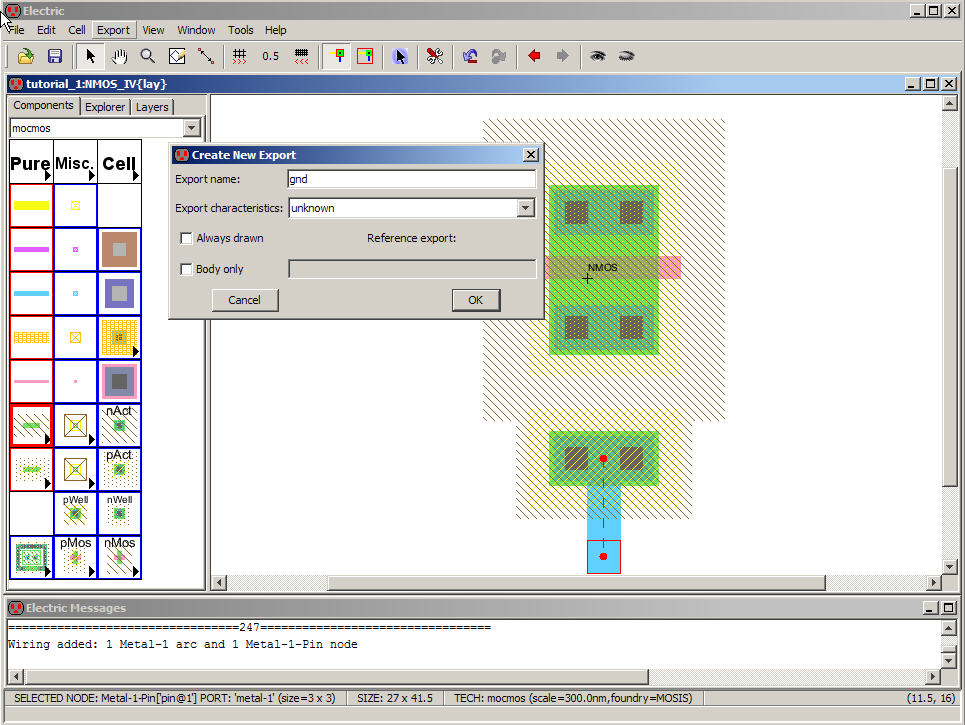

То,

что мы

собираемся

сделать, это

"экспорт" соединения

с p-подложкой

через pWell-компонент

и только что

добавленного

metal1 Arc соединения.

Только

компоненты

могут

экспортироваться,

поэтому мы не

можем

экспортировать

Arc metal1.

Это

означает, что

мы можем

экспортировать

выделенный

вывод (pin)

или узел pWell.

Давайте

экспортируем

pin,

показанный

выше. Если он

не подсвечен,

используйте Ctrl + click,

пока не будет

выбран

нужный вывод.

Когда

pin выбран,

перейдите в

меню и

выберите Export -> Create

Export (или

используйте Ctrl+E)

Дайте

результату

экспорта имя

"gnd"

как показано

ниже. Оставьте характеристики

экспорта

неопределёнными.

Важно

(когда мы

делаем NCC)

использовать

нижний

регистр gnd для

представления

земли (чтобы

соответствовать

символу,

который мы

будем

использовать

для земли в

схеме в

ближайшее

время).

Мы

также будем

использовать

обозначение vdd в

нижнем

регистре,

чтобы

корректно

обозначить

символ входа

питания NCC (aka LVS).

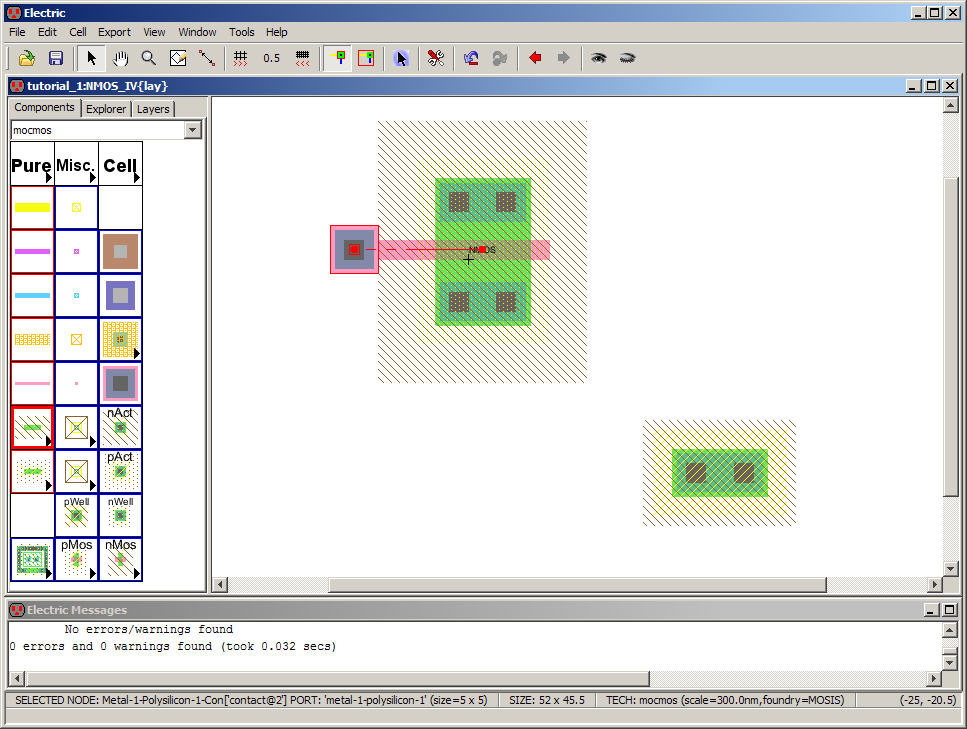

Теперь,

когда мы

проводим

проверку кармана

транзистора,

мы не

получаем

ошибок (см.

Окно "Electric

Message" ниже).

Давайте

добавим metal1 Arc

металлизацию

для

остальных

трёх MOSFET

выходов

и сделаем

экспорт, как

делали выше.

Убедимся,

что DRC и ERC-контроль

проходит.

Также

убедимся, что

все контакты

экспортированы.

Если

вы

попытаетесь

добавить Arc-соединение

в области

истока-стока

и использовать

n-канальную

область,

перейдите в

меню и выберите

metal1, как

показано

ниже.

Не

забудьте

сохранить

результаты

вашей работы!

Мы

можем

использовать

ту же

последовательность

действий,

чтобы

создать

ячейку PMOS_IV.

Ниже

представлен

сокращенный

набор инструкций,

поскольку

процесс и так

понятен.

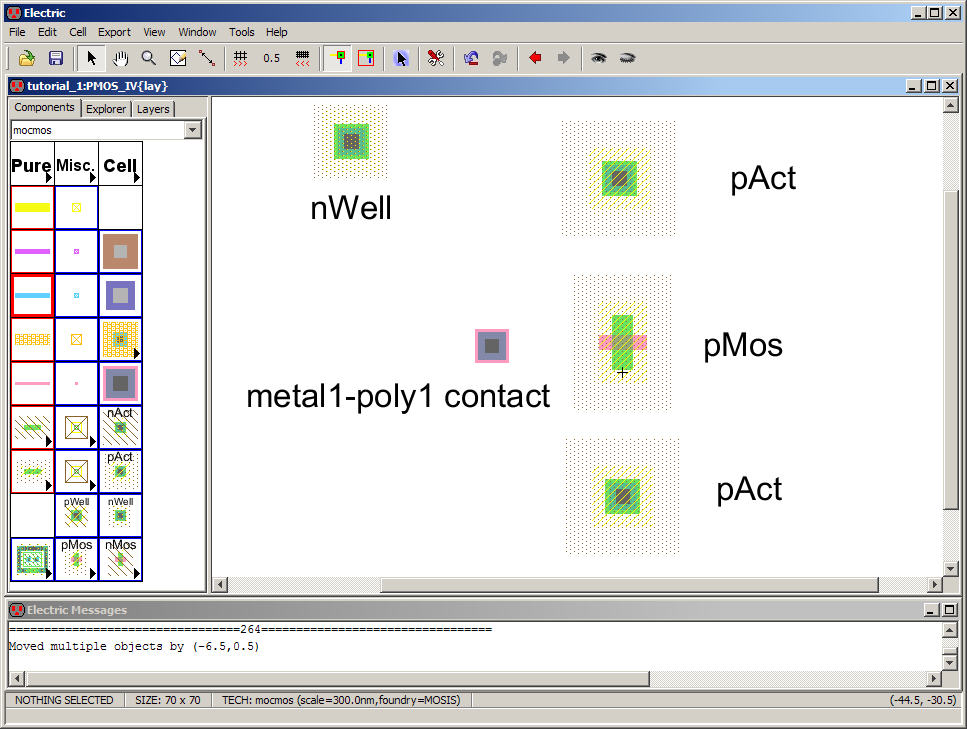

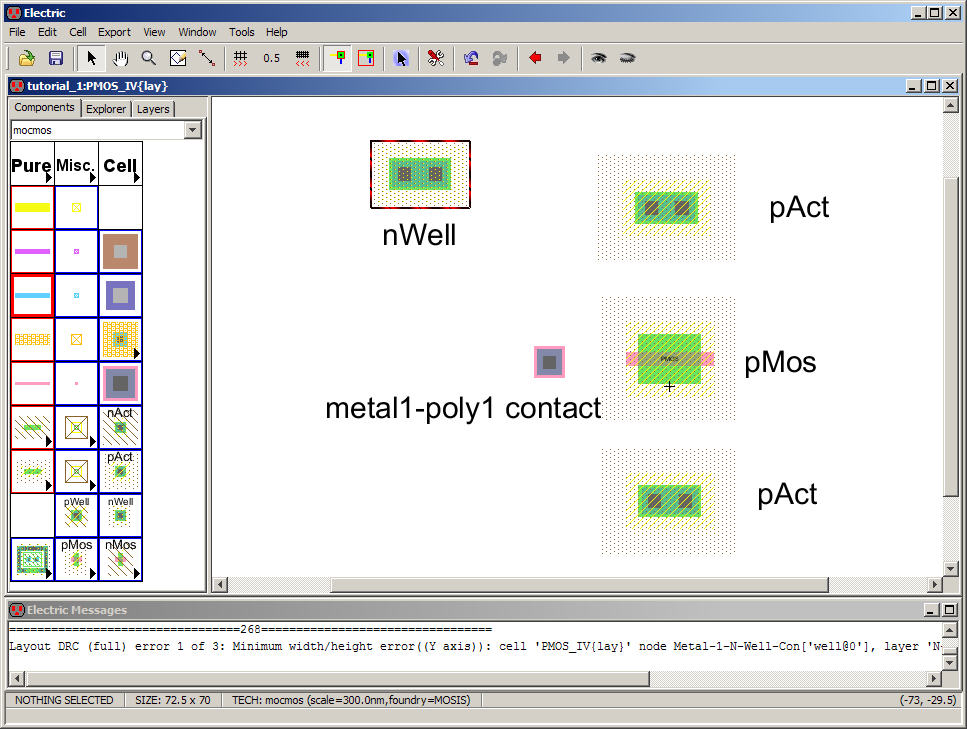

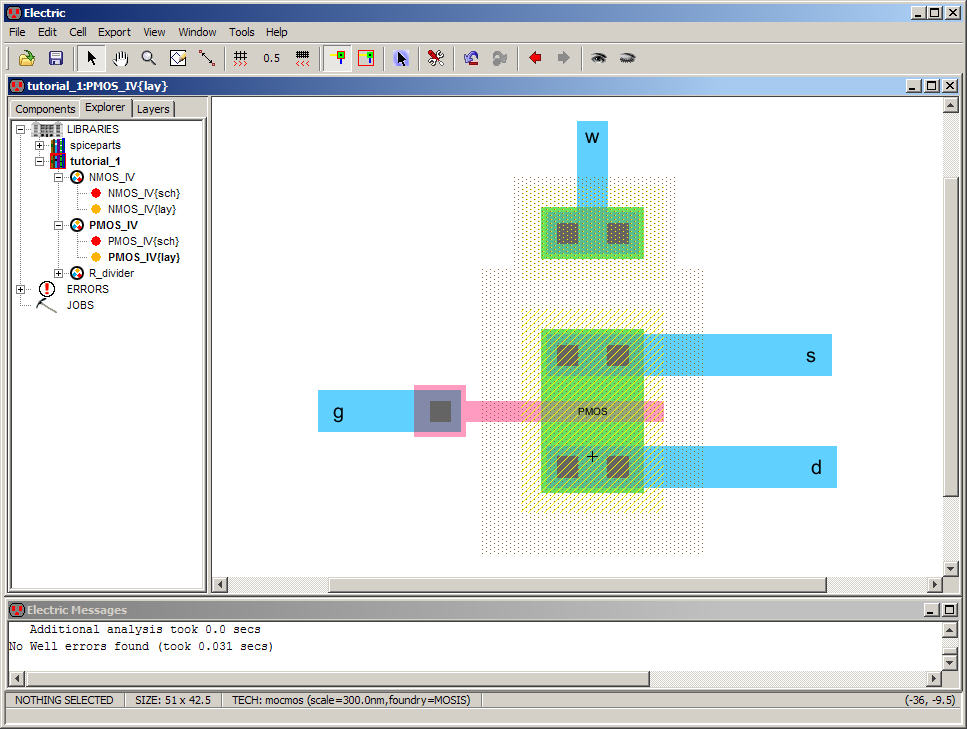

Перейдите

в PMOS_IV{lay} и

добавьте

необходимые

элементы.

Change the width of the nMos Node to 10 and

the x-size of the remaining Nodes to 10 with the exception the metal1-poly1

contact Node.

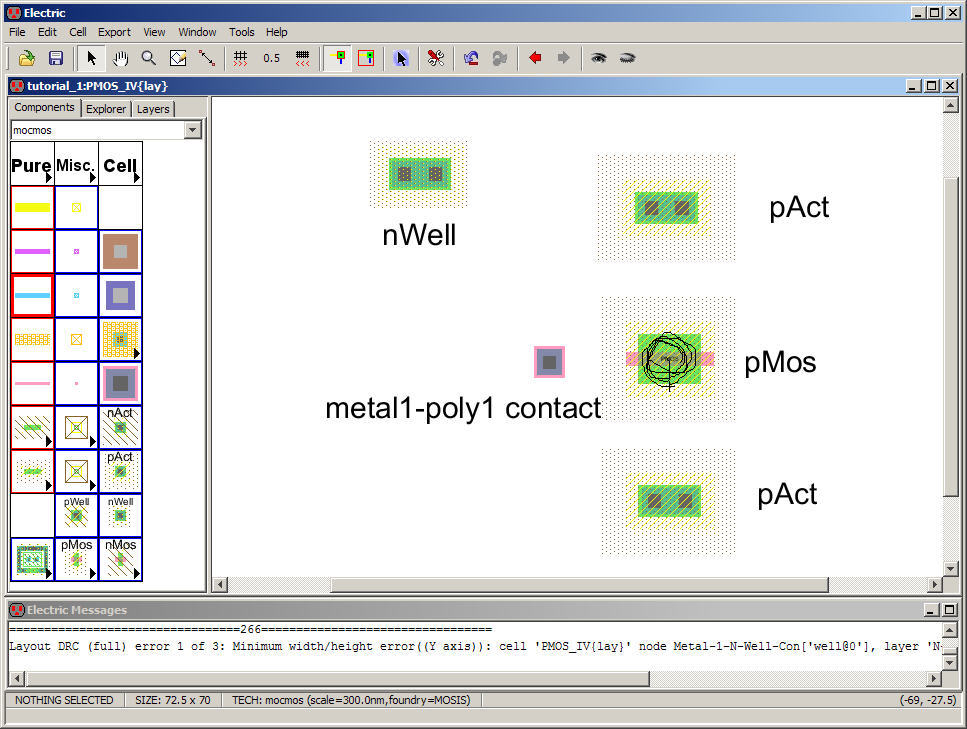

Next select the pMos Node and go to the menu,

Tools �> Simulation (Spice) -> Set Spice Model� and set the PMOS�s

SPICE model to PMOS.

Important if we want to simulate the layout (and we do!)

The result of these actions is seen below where the SPICE model name has

been circled since it�s hard to see.

If we perform a DRC check on this layout we get the following error (the

nWell isn�t tall enough).

Change the y-size of the nWell Node so that

it�s 6.

You may have additional well errors if you�ve placed your Nodes too

close together.

All of these errors disappear after the Nodes are connected together.

Let�s connect them together now, export the Pins, and delete the

Annotation text as seen below.

Проведите

DRC и

ERC Well проверку.

Ошибок

быть не

должно.

Обратите

внимание, что

мы могли бы

внести путаницу,

назвав

металлические

контакты (d, g, s и w)

путём выбора Arc и

редактирования

свойств с

помощью Ctrl + I), т.е.

вместо экспорта

внешних контактов.

Это

может

показаться

излишним

сейчас, но

важно, когда

вы быстро

продвигаетесь

и сразу же

именуете

контакты, чтобы

данные

моделирования

было легче

понимать.

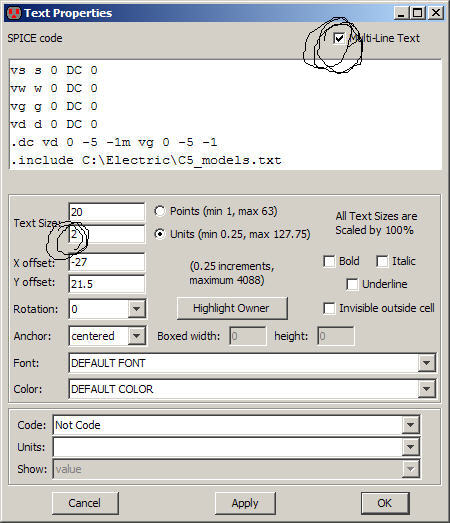

Мы

готовы к

моделированию.

Перейдите

в меню Component

и

выберите

стрелку под Misc, чтобы

получить

доступ к Spice

Code.

Добавьте

код Spice,

указанный

ниже, при

условии, что

вы используете

многострочный

текст, а

размер текста

увеличен до 2.

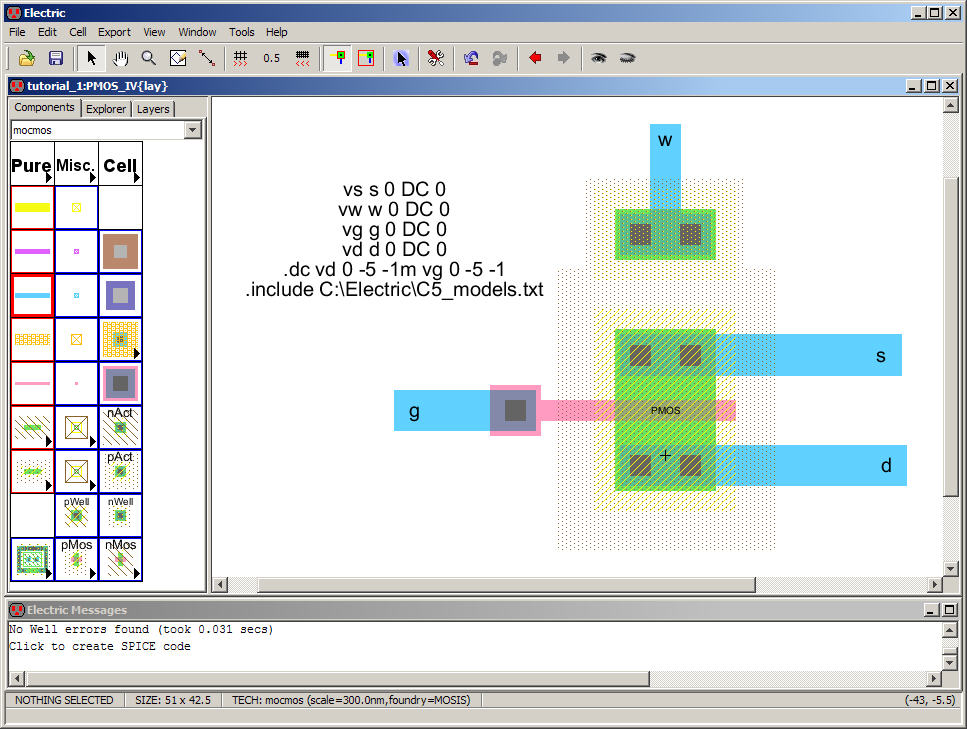

Элемент

теперь будет

выглядеть

так, как показано

ниже.

Обратите

внимание:

если вы не

сохранили

модель C5 в вашем

рабочем

каталоге, как

обсуждалось в

начале этого

руководства,

моделирование

не будет

работать

(правильно).

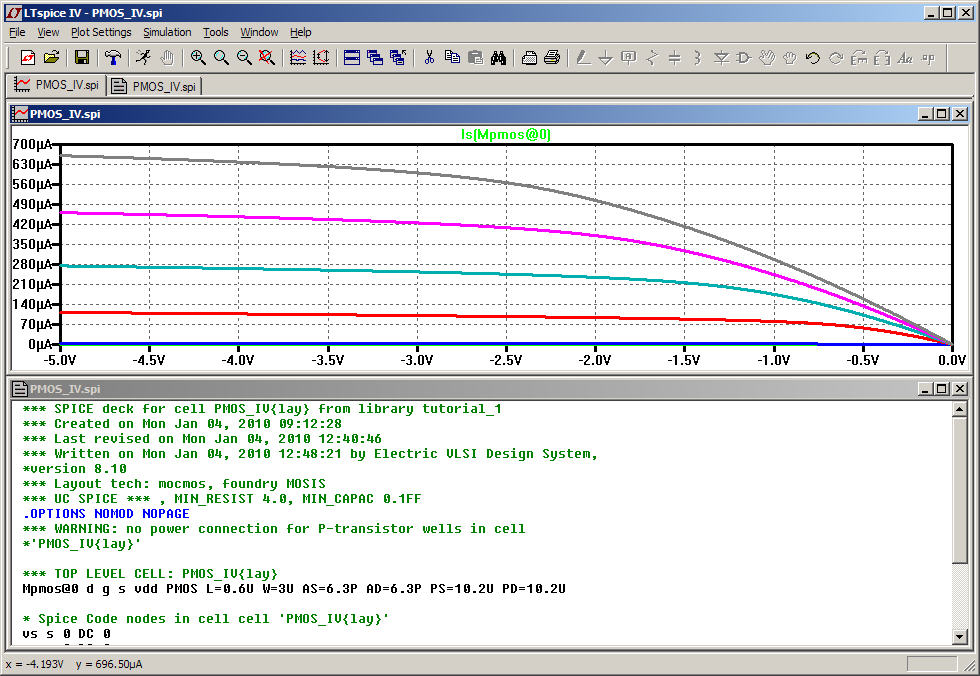

Перейдите в меню Tools ->

Simulation (Spice) -> Write Spice Deck

Это приводёт

к следующему

(опять же,

предполагая,

что у вас

есть

правильно

настроенная

программа LTspice)

построению

графиков

тока стока

для устройства

PMOS:

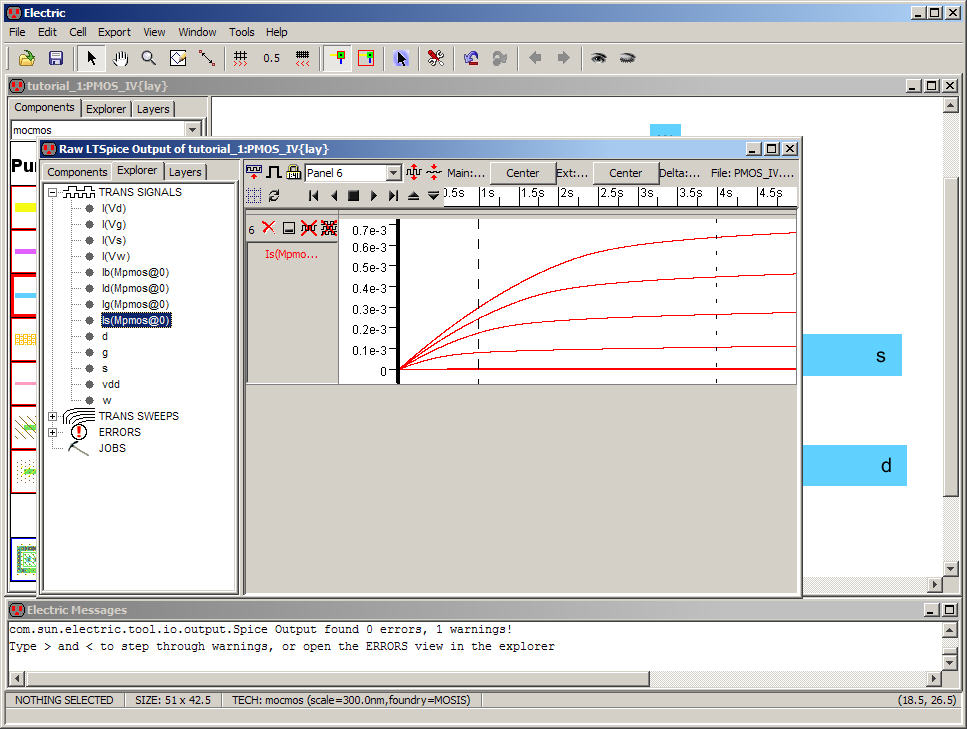

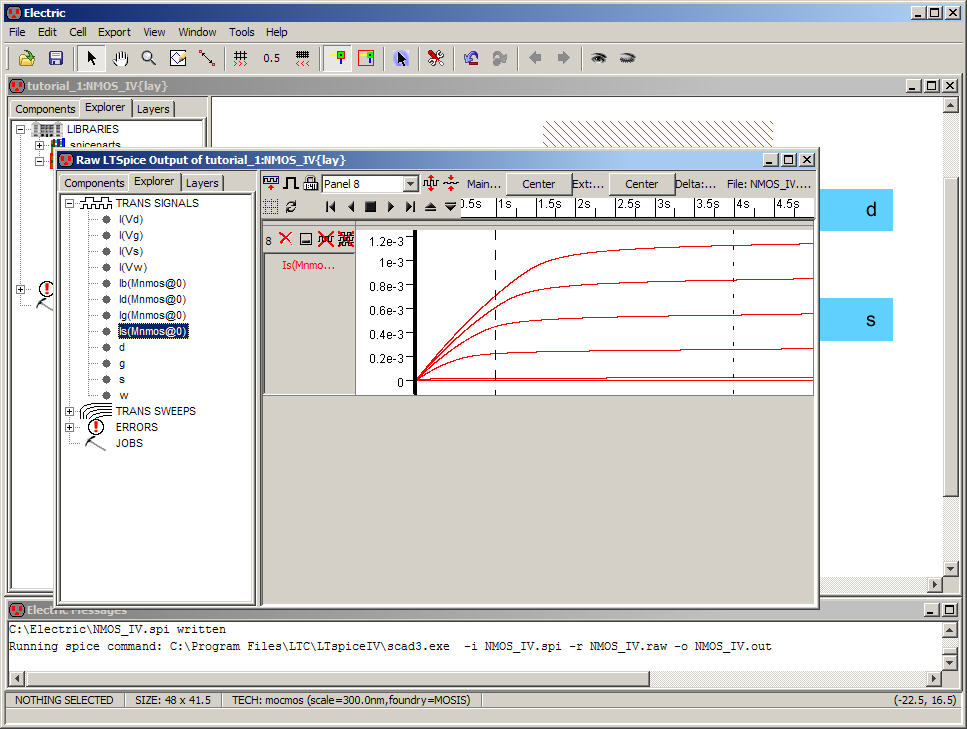

or using Electric�s probe which should run after you�ve closed

LTspice (of course you have to use the Explorer to select the right signals).

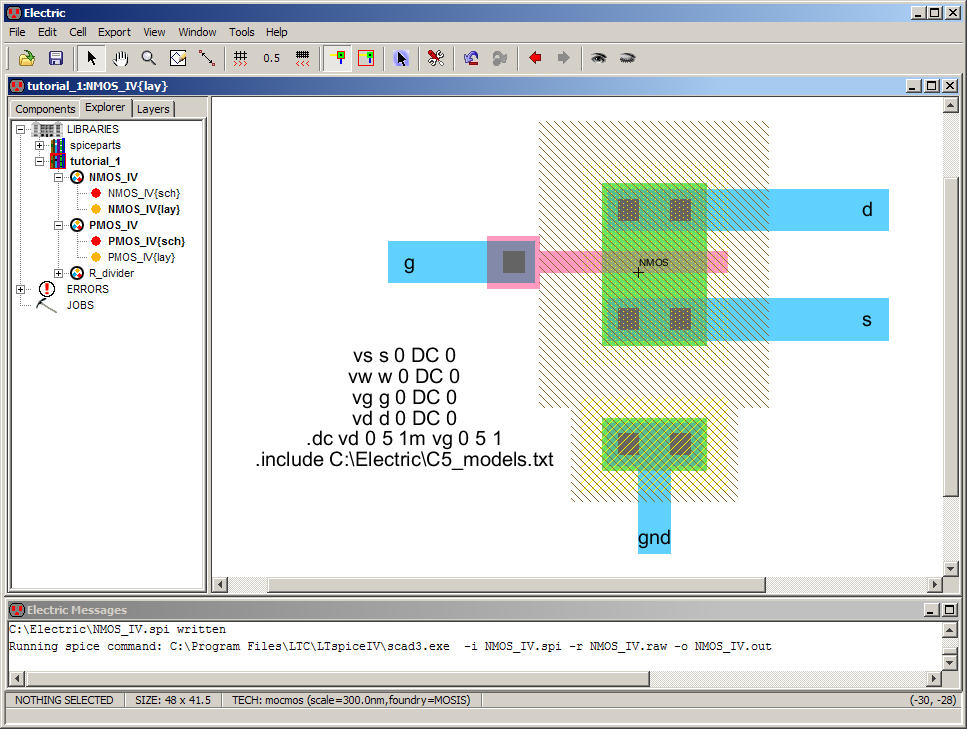

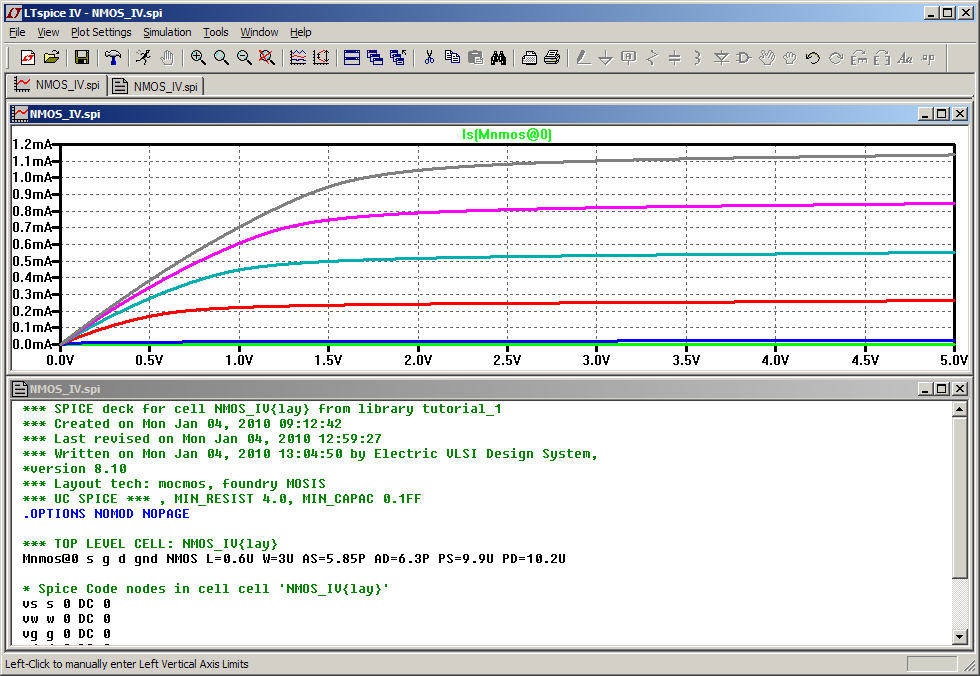

Adding similar Spice Code to our NMOS_IV{lay} view results in

With simulation results from LTspice

and using Electric�s probe

The last step is to finish up the schematics so the layout and schematic

NCC without errors.

Copy the Spice code from NMOS_IV{lay} to NMOS_IV{sch}

and change the text�s size from 2 to 0.5.

Repeat for the PMOS_IV cells.

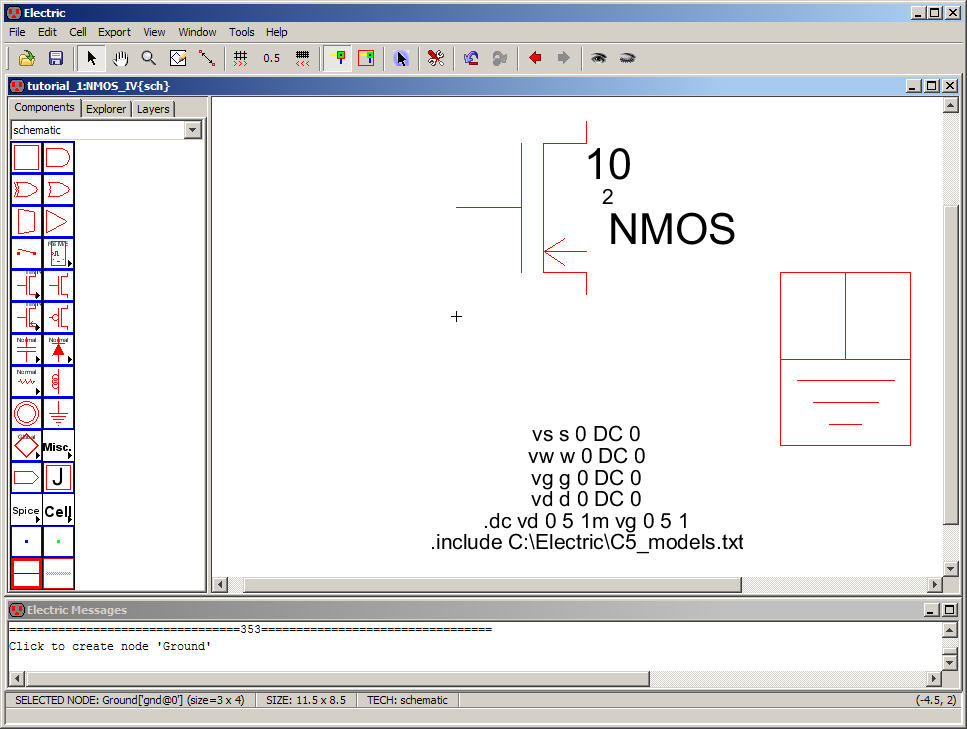

Go back to the NMOS_IV{sch} cell and

select/place the ground symbol from the Component menu on the left, see below.

The ground Node symbol is a little large, relative the MOSFET symbol, so

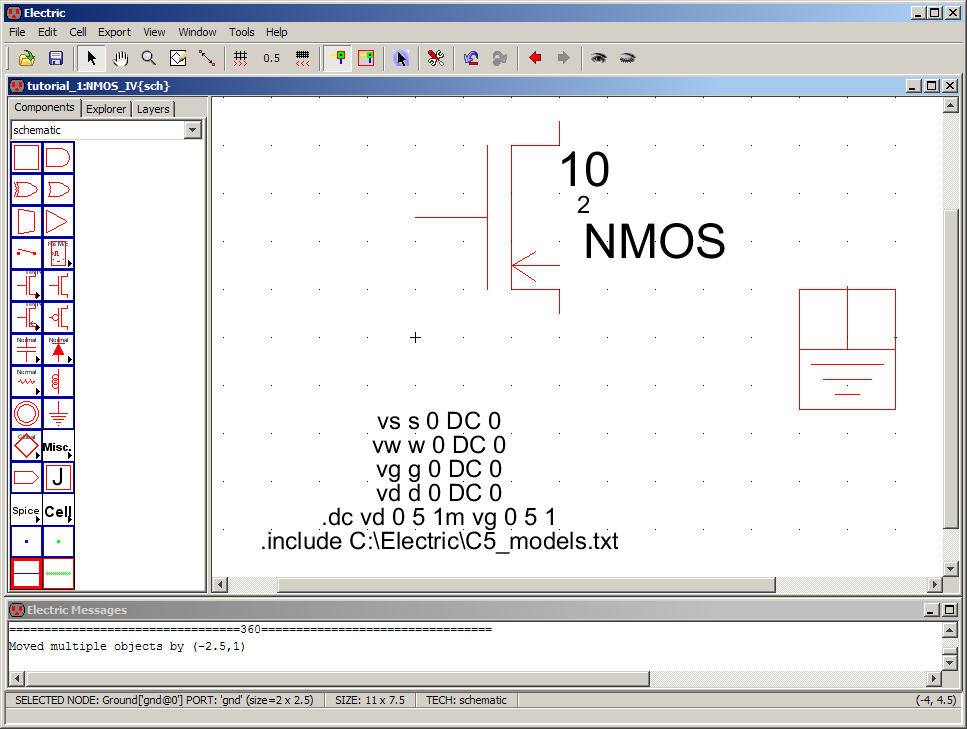

let�s shrink it.

First turn the Grid on by pressing Ctrl+G or

Window -> Toggle Grid

With this ground Node active go to Edit -> Size -> Interactively

or just press Ctrl+B

Adjust the size so that the ground Node is smaller and its single port

at the top of the symbol stays on Grid, see below.

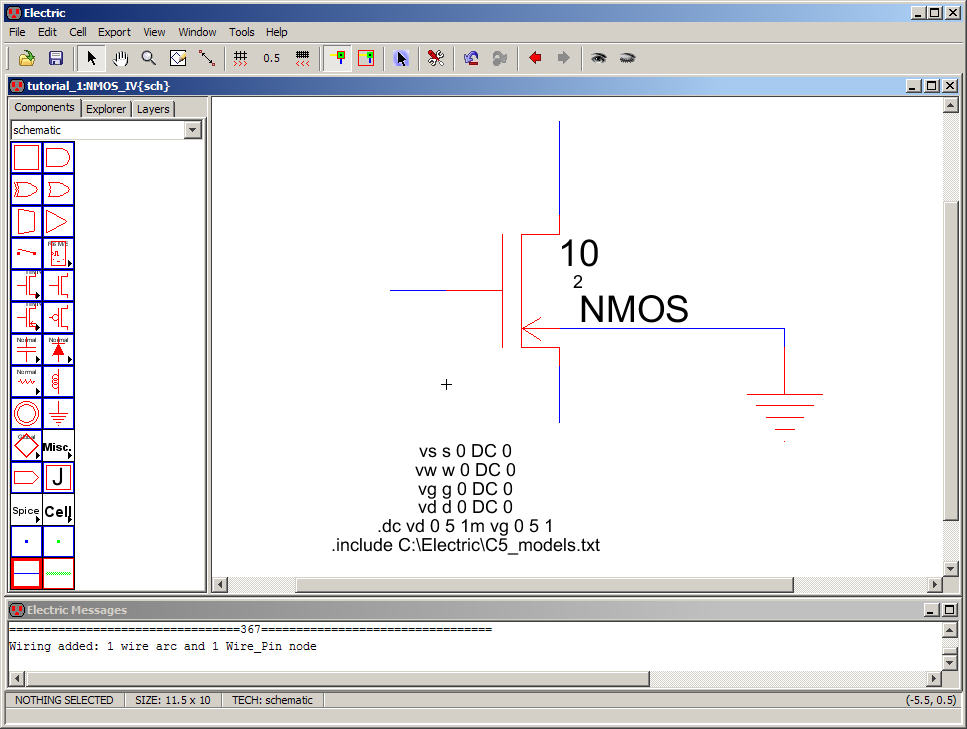

Next turn off the grid and add wire Arcs to get the following.

We need to export Pins to make the schematic/layout NCC correctly

To see the Pins let�s draw a box around everything, as seen below.

If this doesn�t work make sure that you have the Select Objects button

(circled below) enabled (not the Select Area)

Using Export -> Create Export (or better yet Ctrl+E)

export the appropriate Pins to match the layout, see below.

Remember to use Ctrl+click for ease of

selection.

Make sure, as in all of these tutorials, that you leave the Export

Characteristics at �unknown�

Note, again, we could confuse ourselves if we named the Arcs with these

names instead of Exporting the Pins

Verify the above schematic matches the layout (perform an NCC)

At this point you can also simulate this schematic (since this is easy

go ahead and do it).

Repeat these steps for the PMOS schematic view.

The end result is seen below.

Again verify that this schematic matches the layout using NCC.

Also, again, this schematic can be simulated (go ahead and do this).

This is the

end of the second tutorial.